6.1 Úvod

Moderné univerzálne počítače sú dvoch typov: CISC a RISC. CISC znamená Complex Instruction Set Computer. RIZIKO znamená Počítač so zníženou inštrukciou. Mikroprocesory 6502 alebo 6510, ktoré sa dajú použiť na počítač Commodore-64, pripomínajú skôr architektúru RISC ako architektúru CISC.

Počítače RISC majú vo všeobecnosti kratšie inštrukcie v jazyku symbolických inštrukcií (podľa počtu bajtov) v porovnaní s počítačmi CISC.

Poznámka : Či už ide o počítač CISC, RISC alebo starý počítač, periférne zariadenie začína interným portom a smeruje von cez externý port na zvislom povrchu systémovej jednotky počítača (základnej jednotky) a k externému zariadeniu.

Typickú inštrukciu počítača CISC možno považovať za spojenie niekoľkých krátkych inštrukcií v jazyku symbolických inštrukcií do jednej dlhšej inštrukcie v jazyku symbolických inštrukcií, vďaka čomu je výsledná inštrukcia komplexná. Najmä počítač CISC načíta operandy z pamäte do registrov mikroprocesora, vykoná operáciu a potom uloží výsledok späť do pamäte, všetko v jednej inštrukcii. Na druhej strane ide o minimálne tri inštrukcie (krátke) pre počítač RISC.

Existujú dva populárne rady počítačov CISC: mikroprocesorové počítače Intel a mikroprocesorové počítače AMD. AMD znamená Advanced Micro Devices; je to spoločnosť vyrábajúca polovodiče. Séria mikroprocesorov Intel v poradí vývoja je 8086, 8088, 80186, 80286, 80386, 80486, Pentium, Core, i Series, Celeron a Xeon. Inštrukcie v jazyku symbolických inštrukcií pre prvé mikroprocesory Intel, ako sú 8086 a 8088, nie sú príliš zložité. Pre nové mikroprocesory sú však zložité. Najnovšie mikroprocesory AMD pre sériu CISC sú Ryzen, Opteron, Athlon, Turion, Phenom a Sempron. Mikroprocesory Intel a AMD sú známe ako mikroprocesory x86.

ARM je skratka pre Advanced RISC Machine. Architektúry ARM definujú rodinu RISC procesorov, ktoré sú vhodné na použitie v širokej škále aplikácií. Zatiaľ čo mnoho mikroprocesorov Intel a AMD sa používa v stolných osobných počítačoch, mnohé procesory ARM slúžia ako vstavané procesory v systémoch kritických z hľadiska bezpečnosti, ako sú automobilové protiblokovacie brzdy a ako univerzálne procesory v inteligentných hodinkách, prenosných telefónoch, tabletoch a prenosných počítačoch. . Hoci oba typy mikroprocesorov možno vidieť v malých aj veľkých zariadeniach, mikroprocesory RISC sa nachádzajú skôr v malých zariadeniach ako vo veľkých zariadeniach.

Počítačové slovo

Ak sa o počítači hovorí, že je to počítač s 32-bitovým slovom, znamená to, že informácie sú uložené, prenášané a manipulované vo forme 32-bitových binárnych kódov vo vnútornej časti základnej dosky. Znamená to tiež, že všeobecné registre v mikroprocesore počítača majú šírku 32 bitov. Registre A, X a Y mikroprocesora 6502 sú registre na všeobecné použitie. Sú osembitové, takže počítač Commodore-64 je osembitový slovný počítač.

Nejaká slovná zásoba

Počítače X86

Významy byte, word, doubleword, quadword a double-quadword sú pre počítače x86 nasledovné:

- Byte : 8 bitov

- Slovo : 16 bitov

- Doubleword : 32 bitov

- Quadword : 64 bitov

- Dvojité štvorslovie : 128 bitov

Počítače ARM

Významy byte, halfword, word a doubleword sú pre počítače ARM nasledovné:

- Byte : 8 bitov

- Staňte sa polovicou : 16 bitov

- Slovo : 32 bitov

- Doubleword : 64 bitov

Treba poznamenať rozdiely a podobnosti názvov x86 a ARM (a hodnôt).

Poznámka : Znamenkové celé čísla v oboch typoch počítačov sú doplnkom dvoch.

Umiestnenie pamäte

S počítačom Commodore-64 je pamäťové miesto zvyčajne jeden bajt, ale príležitostne môžu byť dva po sebe idúce bajty, keď sa zvažujú ukazovatele (nepriame adresovanie). V modernom počítači x86 je pamäťové miesto 16 po sebe idúcich bajtov pri práci s dvojitým štvorslovom 16 bajtov (128 bitov), 8 po sebe idúcich bajtov pri práci so štvorslovom 8 bajtov (64 bitov), 4 po sebe idúce bajty pri práci s dvojslovom 4 bajty (32 bitov), 2 po sebe idúce bajty pri práci s 2 bajtovým slovom (16 bitov) a 1 bajt pri práci s bajtom (8 bitov). V modernom počítači ARM je pamäťové miesto 8 po sebe idúcich bajtov pri práci s dvojslovom 8 bajtov (64 bitov), 4 po sebe idúce bajty pri práci so slovom 4 bajtov (32 bitov), 2 po sebe idúce bajty pri práci s polslovom 2 bajty (16 bitov) a 1 bajt pri práci s bajtom (8 bitov).

Táto kapitola vysvetľuje, čo je spoločné v architektúrach CISC a RISC a aké sú ich rozdiely. Toto sa robí v porovnaní s 6502 µP a počítačom commodore-64, kde je to použiteľné.

6.2 Bloková schéma základnej dosky moderného počítača

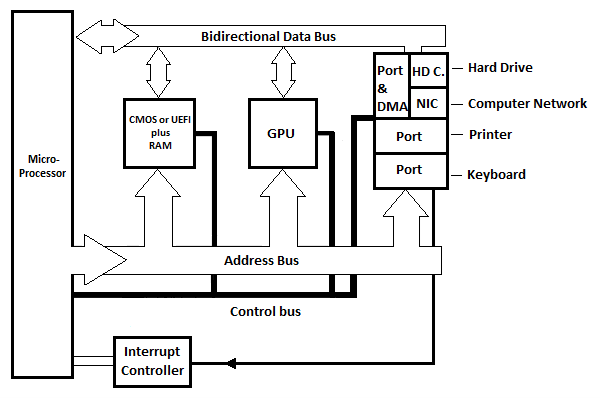

PC je skratka pre osobný počítač. Nasleduje všeobecná základná bloková schéma modernej základnej dosky s jedným mikroprocesorom pre osobný počítač. Predstavuje základnú dosku CISC alebo RISC.

Obr. 6.21 Základná bloková schéma základnej dosky moderného PC

Na obrázku sú znázornené tri interné porty, ale v praxi je ich viac. Každý port má register, ktorý možno považovať za samotný port. Každý obvod portu má aspoň ďalší register, ktorý možno nazvať „stavový register“. Stavový register označuje port programu, ktorý vysiela signál prerušenia do mikroprocesora. Existuje obvod regulátora prerušenia (nie je znázornený), ktorý rozlišuje medzi rôznymi prerušovacími linkami z rôznych portov a má len niekoľko liniek k µP.

HD.C v diagrame znamená Hard Drive Card. NIC je skratka pre Network Interface Card. Karta pevného disku (obvod) je pripojená k pevnému disku, ktorý je vo vnútri základnej jednotky (systémovej jednotky) moderného počítača. Sieťová karta (obvod) je pripojená cez externý kábel k inému počítaču. Na obrázku je jeden port a DMA (pozrite si nasledujúci obrázok), ktoré sú pripojené ku karte pevného disku a/alebo ku karte sieťového rozhrania. DMA znamená priamy prístup do pamäte.

V kapitole o počítačoch Commodore-64 si pamätajte, že na odoslanie bajtov z pamäte na diskovú jednotku alebo iný počítač sa každý bajt musí skopírovať do registra v mikroprocesore pred skopírovaním na príslušný interný port a potom automaticky k zariadeniu. Aby bolo možné prijať bajty z diskovej jednotky alebo iného počítača do pamäte, každý bajt musí byť skopírovaný z príslušného interného registra portu do registra mikroprocesora pred skopírovaním do pamäte. To zvyčajne trvá dlho, ak je počet bajtov v streame veľký. Riešením pre rýchly prenos je použitie Direct Memory Access (obvodu) bez prechodu cez mikroprocesor.

Obvod DMA je medzi portom a HD. C alebo NIC. S priamym prístupom do pamäte obvodu DMA je prenos veľkých prúdov bajtov priamo medzi obvodom DMA a pamäťou (RAM) bez pokračujúcej účasti mikroprocesora. DMA používa namiesto µP adresovú zbernicu a dátovú zbernicu. Celkové trvanie prenosu je kratšie, ako keby sa mal použiť µP hard. HD C. aj NIC používajú DMA, keď majú veľký tok dát (bajtov) na prenos s RAM (pamäťou).

GPU je skratka pre Graphics Processing Unit. Tento blok na základnej doske je zodpovedný za odosielanie textu a pohyblivých alebo statických obrázkov na obrazovku.

V moderných počítačoch (PC) nie je žiadna pamäť iba na čítanie (ROM). Existuje však BIOS alebo UEFI, čo je druh energeticky nezávislej pamäte RAM. Informácie v systéme BIOS sú v skutočnosti udržiavané batériou. Batéria je to, čo v skutočnosti udržuje aj časovač hodín v správnom čase a dátume pre počítač. UEFI bolo vynájdené po BIOSe a nahradilo BIOS, hoci BIOS je stále dosť relevantný v moderných počítačoch. Viac o nich budeme diskutovať neskôr!

V moderných počítačoch nie sú adresové a dátové zbernice medzi µP a internými obvodmi portu (a pamäťou) paralelnými zbernicami. Sú to sériové zbernice, ktoré potrebujú dva vodiče na prenos v jednom smere a ďalšie dva vodiče na prenos v opačnom smere. To znamená, že napríklad 32 bitov možno posielať v sérii (jeden bit za druhým) v oboch smeroch.

Ak je sériový prenos iba v jednom smere s dvoma vodičmi (dve linky), hovorí sa, že ide o polovičný duplex. Ak je sériový prenos v oboch smeroch so štyrmi vodičmi, jedným párom v každom smere, hovorí sa, že je to plne duplexný.

Celá pamäť moderného počítača stále pozostáva zo série bajtových umiestnení: osem bitov na bajt. Moderný počítač má pamäťový priestor najmenej 4 gigabajty = 4 x 210 x 2 10 x 2 10 = 4 x 1 073 741 824 10 bajtov = 4 x 1024 10/sub> x 1024 10 x 1024 10 = 4 x 1 073 741 824 10 .

Poznámka : Hoci na predchádzajúcej základnej doske nie je zobrazený žiadny obvod časovača, všetky moderné základné dosky majú obvody časovača.

6.3 Základy počítačovej architektúry x64

6.31 Súprava registrov x64

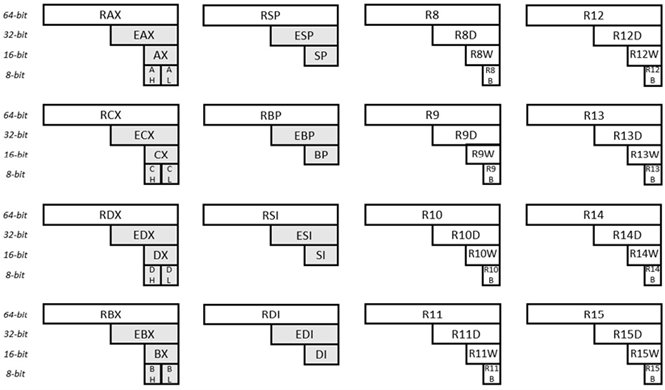

64-bitový mikroprocesor zo série mikroprocesorov x86 je 64-bitový mikroprocesor. Nahradiť 32-bitový procesor rovnakej série je celkom moderné. Všeobecné registre 64-bitového mikroprocesora a ich názvy sú nasledovné:

Obr. 6.31 Všeobecné registre pre x64

Na uvedenom obrázku je zobrazených šestnásť (16) registrov na všeobecné použitie. Každý z týchto registrov je široký 64 bitov. Pri pohľade na register v ľavom hornom rohu je 64 bitov identifikovaných ako RAX. Prvých 32 bitov toho istého registra (sprava) je identifikovaných ako EAX. Prvých 16 bitov toho istého registra (sprava) je identifikovaných ako AX. Druhý bajt (sprava) toho istého registra je označený ako AH (H tu znamená vysoký). A prvý bajt (toho istého registra) je identifikovaný ako AL (L tu znamená nízky). Pri pohľade na register v pravom dolnom rohu je 64 bitov označených ako R15. Prvých 32 bitov toho istého registra je identifikovaných ako R15D. Prvých 16 bitov toho istého registra je označených ako R15W. A prvý bajt je označený ako R15B. Názvy ostatných registrov (a podregistrov) sú vysvetlené podobne.

Medzi procesormi Intel a AMD µP sú určité rozdiely. Informácie v tejto časti sú pre Intel.

Pri 6502 µP je register počítadla programov (nie je dostupný priamo), ktorý obsahuje ďalšiu inštrukciu, ktorá sa má vykonať, široký 16 bitov. Tu (x64) sa počítadlo programu nazýva ukazovateľ inštrukcie a má šírku 64 bitov. Je označený ako RIP. To znamená, že x64 µP môže adresovať až 264 = 1,844674407 x 1019 (v skutočnosti 18 446 744 073 709 551 616) pamäťových bajtov. RIP nie je všeobecný register.

Stack Pointer Register alebo RSP patrí medzi 16 všeobecných registrov. Ukazuje na posledný záznam zásobníka v pamäti. Rovnako ako pri 6502 µP, zásobník pre x64 rastie smerom nadol. Pri x64 sa zásobník v RAM používa na ukladanie návratových adries pre podprogramy. Používa sa aj na ukladanie „tieňového priestoru“ (pozri nasledujúcu diskusiu).

6502 µP má 8-bitový stavový register procesora. Ekvivalent v x64 sa nazýva register RFLAGS. V tomto registri sú uložené príznaky, ktoré sa používajú na výsledky operácií a na riadenie procesora (µP). Má šírku 64 bitov. Vyšších 32 bitov je rezervovaných a momentálne sa nepoužívajú. Nasledujúca tabuľka uvádza názvy, index a významy bežne používaných bitov v registri RFLAGS:

| Tabuľka 6.31.1 Najpoužívanejšie RFLAGS vlajky (bity) |

|||

|---|---|---|---|

| Symbol | Trocha | názov | Účel |

| CF | 0 | Prenášať | Nastavuje sa, ak aritmetická operácia generuje prenos alebo požičanie z najvýznamnejšieho bitu výsledku; vymazané inak. Tento príznak označuje stav pretečenia pre aritmetiku celého čísla bez znamienka. Používa sa aj v aritmetike s viacnásobnou presnosťou. |

| PF | 2 | Parita | Nastaví sa, ak najmenej významný bajt výsledku obsahuje párny počet 1 bitov; vymazané inak. |

| OF | 4 | Upraviť | Nastavuje sa, ak aritmetická operácia generuje prenos alebo vypožičanie z bitu 3 výsledku; vymazané inak. Tento príznak sa používa v binárne kódovanej desiatkovej (BCD) aritmetike. |

| ZF | 6 | nula | Nastaví sa, ak je výsledok nula; vymazané inak. |

| SF | 7 | Podpísať | Nastavuje sa, ak sa rovná najvýznamnejšiemu bitu výsledku, ktorý je znamienkovým bitom celého čísla so znamienkom (0 označuje kladnú hodnotu a 1 označuje zápornú hodnotu). |

| OF | jedenásť | Pretečenie | Nastavuje sa, ak je výsledkom celého čísla príliš veľké kladné číslo alebo príliš malé záporné číslo (okrem znamienkového bitu), aby sa zmestilo do cieľového operandu; vymazané inak. Tento príznak označuje podmienku pretečenia pre aritmetiku celého čísla so znamienkom (doplnok dvoch). |

| DF | 10 | Smer | Nastavuje sa, ak fungujú inštrukcie smerového reťazca (inkrementácia alebo dekrementácia). |

| ID | dvadsaťjeden | Identifikácia | Nastavuje sa, ak meniteľnosť označuje prítomnosť inštrukcie CPUID. |

Okrem osemnástich 64-bitových registrov, ktoré boli uvedené vyššie, architektúra x64 µP má osem 80-bitových širokých registrov pre aritmetiku s pohyblivou rádovou čiarkou. Týchto osem registrov možno použiť aj ako registre MMX (pozri nasledujúcu diskusiu). Existuje tiež šestnásť 128-bitových registrov pre XMM (pozri nasledujúcu diskusiu).

To nie je všetko o registroch. Existuje viac registrov x64, ktorými sú segmentové registre (väčšinou nepoužívané v x64), riadiace registre, registre správy pamäte, registre ladenia, virtualizačné registre, registre výkonu, ktoré sledujú všetky druhy interných parametrov (úspešné/nevyužité vyrovnávacie pamäte, vykonané mikrooperácie, časovanie). , a oveľa viac).

SIMD

SIMD znamená Single Instruction Multiple Data. To znamená, že jedna inštrukcia v jazyku symbolických inštrukcií môže pôsobiť na viacero údajov súčasne v jednom mikroprocesore. Zvážte nasledujúcu tabuľku:

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | |

| + | 9 | 10 | jedenásť | 12 | 13 | 14 | pätnásť | 16 |

| = | 10 | 12 | 14 | 16 | 18 | dvadsať | 22 | 24 |

V tejto tabuľke sa paralelne (v rovnakom trvaní) pridá osem párov čísel, čím sa získa osem odpovedí. Jedna inštrukcia jazyka symbolických inštrukcií dokáže vykonať osem paralelných celočíselných sčítaní v registroch MMX. Podobná vec sa dá urobiť s registrami XMM. Takže existujú inštrukcie MMX pre celé čísla a pokyny XMM pre plaváky.

6.32 Mapa pamäte a x64

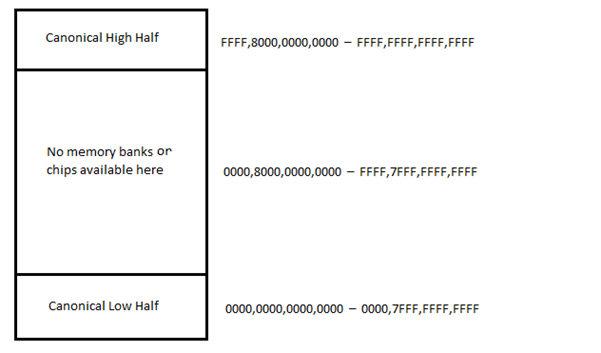

S ukazovateľom inštrukcií (počítadlom programu) so 64 bitmi to znamená, že je možné adresovať 264 = 1,844674407 x 1019 pamäťových bajtov. V šestnástkovej sústave je najvyššie umiestnenie bajtu FFFF,FFFF,FFFF,FFFF16. Žiadny bežný počítač dnes nedokáže poskytnúť takú veľkú pamäť (kompletný) priestor. Takže vhodná mapa pamäte pre počítač x64 je nasledovná:

Všimnite si, že medzera od 0000,8000,0000,000016 do FFFF,7FFF,FFFF,FFFF16 nemá žiadne pamäťové miesta (žiadne pamäťové RAM banky). Toto je rozdiel FFFF, 0000 0000 000 116, čo je dosť veľký. Kanonická vysoká polovica obsahuje operačný systém, zatiaľ čo kanonická nízka polovica obsahuje používateľské programy (aplikácie) a údaje. Operačný systém sa skladá z dvoch častí: malej UEFI (BIOS) a veľkej časti, ktoré sa načítavajú z pevného disku. Ďalšia kapitola hovorí viac o moderných operačných systémoch. Všimnite si podobnosť s touto pamäťovou mapou a pre Commodore-64, keď 64 KB mohlo vyzerať ako veľa pamäte.

V tomto kontexte sa operačný systém nazýva zhruba „kernel“. Jadro je podobné jadru počítača Commodore-64, ale má oveľa viac podprogramov.

Endianness pre x64 je little endian, čo znamená, že pre umiestnenie nižšia adresa ukazuje na nižší obsahový bajt v pamäti.

6.33 Režimy adresovania v assembleri pre x64

Režimy adresovania sú spôsoby, ktorými môže inštrukcia pristupovať k registrom µP a pamäti (vrátane registrov interných portov). x64 má veľa režimov adresovania, ale tu sú adresované iba bežne používané režimy adresovania. Všeobecná syntax pre inštrukciu je tu:

cieľ operačného kódu, zdroj

Desatinné čísla sa píšu bez predpony alebo prípony. Pri 6502 je zdroj implicitný. x64 má viac operačných kódov ako 6502, ale niektoré z operačných kódov majú rovnaké mnemotechnické pomôcky. Jednotlivé x64 inštrukcie majú premenlivú dĺžku a môžu mať veľkosť od 1 do 15 bajtov. Bežne používané režimy adresovania sú nasledovné:

Režim okamžitého adresovania

Zdrojový operand je tu skutočná hodnota a nie adresa alebo štítok. Príklad (prečítajte si komentár):

PRIDAŤ EAX, 14 ; pridajte desatinné číslo 14 do 32-bitového EAX 64-bitového RAX, odpoveď zostane v EAX (cieľ)

Zaregistrujte sa do režimu registrácie adresovania

Príklad:

PRIDAŤ R8B, AL ; pridať 8-bitový AL RAX k R8B 64-bitovému R8 – odpovede zostávajú v R8B (cieľ)

Režim nepriameho a indexovaného adresovania

Nepriame adresovanie s 6502 µP znamená, že umiestnenie danej adresy v inštrukcii má efektívnu adresu (ukazovateľ) konečného miesta. Podobná vec sa stane s x64. Indexové adresovanie s 6502 µP znamená, že obsah registra µP je pridaný k danej adrese v inštrukcii, aby mal účinnú adresu. Podobná vec sa stane s x64. Pri x64 je tiež možné obsah registra pred pridaním k danej adrese vynásobiť 1 alebo 2 alebo 4 alebo 8. Inštrukcia mov (copy) x64 môže kombinovať nepriame aj indexované adresovanie. Príklad:

MOV R8W, 1234[8*RAX+RCX] ; presunúť slovo na adresu (8 x RAX + RCX) + 1234

Tu má R8W prvých 16 bitov R8. Uvedená adresa je 1234. Register RAX má 64-bitové číslo, ktoré sa vynásobí 8. Výsledok sa pripočíta k obsahu 64-bitového registra RCX. Tento druhý výsledok sa pripočíta k danej adrese, ktorá je 1234, aby sa získala efektívna adresa. Číslo v mieste efektívnej adresy sa presunie (skopíruje) na prvé 16-bitové miesto (R8W) v registri R8 a nahradí všetko, čo tam bolo. Všimnite si použitie hranatých zátvoriek. Pamätajte, že slovo v x64 má šírku 16 bitov.

RIP relatívne adresovanie

Pre 6502 µP sa relatívne adresovanie používa iba s inštrukciami vetvenia. Tam je jediným operandom operačného kódu posun, ktorý sa pridáva alebo odčítava od obsahu programového čítača pre efektívnu adresu inštrukcie (nie dátovú adresu). Podobná vec sa stane s x64, kde sa programové počítadlo nazýva ako ukazovateľ inštrukcií. Inštrukcia s x64 nemusí byť len inštrukcia vetvy. Príkladom adresovania relatívneho k RIP je:

MOV AL, [RIP]

AL RAX má 8-bitové číslo so znamienkom, ktoré sa pripočítava alebo odčítava od obsahu v RIP (64-bitový ukazovateľ inštrukcie), aby ukázal na ďalšiu inštrukciu. Všimnite si, že zdroj a cieľ sú v tejto inštrukcii výnimočne zamenené. Všimnite si tiež použitie hranatých zátvoriek, ktoré odkazujú na obsah RIP.

6.34 Bežne používané pokyny x64

V nasledujúcej tabuľke * znamená rôzne možné prípony podmnožiny operačných kódov:

| Tabuľka 6.34.1 Bežne používané pokyny v x64 |

|

|---|---|

| Operačný kód | Význam |

| MOV | Presun (kopírovanie) do/z/medzi pamäťou a registrami |

| CMOV* | Rôzne podmienené pohyby |

| XCHG | Výmena |

| BSWAP | Výmena bajtov |

| PUSH/POP | Použitie zásobníka |

| ADD/ADC | Pridať/s prenosom |

| SUB/SBC | Odčítajte/s prenášaním |

| MUL/IMUL | Násobiť/nepodpísať |

| DIV/IDIV | Rozdeliť/nepodpísané |

| INC/DEC | Zvýšenie/zníženie |

| NEG | Negovať |

| CMP | Porovnaj |

| A/ALEBO/XOR/NIE | Bitové operácie |

| SHR/SAR | Shift doprava logický/aritmetický |

| SHL/SAL | Logický/aritmetický Shift doľava |

| ROR/ROLE | Otočiť doprava/doľava |

| RCR/RCL | Otočte doprava/doľava cez nosný bit |

| BT/BTS/BTR | Bitový test/a nastavenie/a reset |

| ŽMP | Bezpodmienečný skok |

| JE/JNE/JC/JNC/J* | Skákať, ak sa rovná/nerovná sa/nesie/nenesie/mnoho iných |

| PRECHÁDZAŤ/PRACOVAŤ/PRACOVAŤ | Slučka s ECX |

| ZAVOLAŤ/VYPNÚŤ | Volať podprogram/návrat |

| NOP | Žiadna operácia |

| CPUID | informácie o CPU |

x64 má inštrukcie na násobenie a delenie. Vo svojom µP má hardvérové obvody na násobenie a delenie. 6502 µP nemá násobiace a deliace hardvérové obvody. Je rýchlejšie vykonať násobenie a delenie hardvérom ako softvérom (vrátane posúvania bitov).

Pokyny pre reťazec

Existuje množstvo reťazcových inštrukcií, ale jediná, o ktorej tu treba diskutovať, je inštrukcia MOVS (pre presun reťazca) na kopírovanie reťazca začínajúceho na adrese C000. H . Začnite na adrese C100 H , použite nasledujúci návod:

MOVS [C100H], [C000H]

Všimnite si príponu H pre šestnástkovú sústavu.

6.35 Slučovanie v x64

6502 µP má pokyny vetvenia pre slučkovanie. Inštrukcia vetvy preskočí na adresu, ktorá má novú inštrukciu. Umiestnenie adresy sa môže nazývať „slučka“. x64 má inštrukcie LOOP/LOOPE/LOOPNE na zacyklenie. Tieto vyhradené slová v jazyku symbolických inštancií sa nesmú zamieňať so štítkom „slučka“ (bez úvodzoviek). Správanie je nasledovné:

LOOP znižuje ECX a kontroluje, či ECX nie je nula. Ak je táto podmienka (nula) splnená, preskočí sa na určený štítok. V opačnom prípade to prepadne (pokračujte zvyškom pokynov v nasledujúcej diskusii).

LOOPE znižuje ECX a kontroluje, či ECX nie je nula (môže byť napríklad 1) a ZF je nastavené (na 1). Ak sú tieto podmienky splnené, skočí na štítok. V opačnom prípade to prepadne.

LOOPNE zníži ECX a skontroluje, či ECX nie je nula a ZF NIE JE nastavené (t. j. je nulové). Ak sú tieto podmienky splnené, preskočí na štítok. V opačnom prípade to prepadne.

Pri x64 obsahuje register RCX alebo jeho podčasti ako ECX alebo CX celé číslo počítadla. S inštrukciami LOOP počítadlo normálne odpočítava, pričom sa znižuje o 1 pre každý skok (slučku). V nasledujúcom segmente cyklického kódu sa číslo v registri EAX zvyšuje z 0 na 10 v desiatich iteráciách, zatiaľ čo číslo v ECX sa 10-krát odpočítava (znižuje) (prečítajte si komentáre):

MOV EAX, 0 ;

MOV ECX, 10 ; predvolene odpočítajte 10-krát, raz pre každú iteráciu

štítok:

INC EAX; inkrementovať EAX ako telo slučky

štítok LOOP ; znížte EAX a ak EAX nie je nula, znova spustite telo slučky z „label:“

Slučkové kódovanie začína od „label:“. Všimnite si použitie dvojbodky. Slučkové kódovanie končí „LOOP label“, ktorý hovorí dekrementovať EAX. Ak jej obsah nie je nula, vráťte sa k inštrukcii za „label:“ a vykonajte všetky inštrukcie (všetky hlavné pokyny), ktoré idú smerom nadol, až po „LOOP label“. Upozorňujeme, že „štítok“ môže mať stále iný názov.

6.36 Vstup/výstup x64

Táto časť kapitoly sa zaoberá odosielaním údajov na výstupný (interný) port alebo prijímaním údajov zo vstupného (interného) portu. Čipset má osembitové porty. Akékoľvek dva po sebe idúce 8-bitové porty môžu byť považované za 16-bitový port a akékoľvek štyri po sebe idúce porty môžu byť 32-bitovým portom. Týmto spôsobom môže procesor preniesť 8, 16 alebo 32 bitov do alebo z externého zariadenia.

Informácie možno prenášať medzi procesorom a interným portom dvoma spôsobmi: pomocou takzvaného vstup/výstup mapovaný do pamäte alebo pomocou samostatného adresného priestoru vstupu/výstupu. Pamäťovo mapované I/O sú ako to, čo sa deje s procesorom 6502, kde sú adresy portov v skutočnosti súčasťou celého pamäťového priestoru. V tomto prípade pri odosielaní dát na konkrétne miesto adresy idú na port a nie do pamäťovej banky. Porty môžu mať samostatný I/O adresný priestor. V tomto druhom prípade majú všetky pamäťové banky svoje adresy od nuly. Existuje samostatný rozsah adries od 0000H do FFFF16. Tie využívajú porty v čipovej súprave. Základná doska je naprogramovaná tak, aby nedošlo k zámene medzi pamäťovo mapovanými I/O a samostatným I/O adresným priestorom.

Pamäťovo mapované I/O

V tomto prípade sa porty považujú za miesta v pamäti a normálne operačné kódy, ktoré sa majú použiť medzi pamäťou a µP, sa používajú na prenos údajov medzi µP a portami. Ak teda chcete presunúť bajt z portu na adrese F000H do registra µP RAX:EAX:AX:AL, postupujte takto:

MOV AL, [F000H]

Reťazec možno presunúť z pamäte do portu a naopak. Príklad:

MOVS [F000H], [C000H]; zdroj je C000H a cieľ je port na F000H.

Oddelený I/O adresný priestor

Pritom je potrebné použiť špeciálne inštrukcie pre vstup a výstup.

Prenos jednotlivých položiek

Procesorový register na prenos je RAX. V skutočnosti je to RAX:EAX pre dvojité slovo, RAX:EAX:AX pre slovo a RAX:EAX:AX:AL pre bajt. Ak teda chcete preniesť bajt z portu na FFF0h do RAX:EAX:AX:AL, zadajte nasledovné:

V AL, [FFF0H]

Pre spätný prevod zadajte nasledovné:

OUT [FFF0H], AL

Takže pre jednotlivé položky sú pokyny IN a OUT. Adresu portu je možné zadať aj v registri RDX:EDX:DX.

Prenos reťazcov

Reťazec možno preniesť z pamäte do portu čipovej sady a naopak. Ak chcete preniesť reťazec z portu na adrese FFF0H do pamäte, začnite na C100H, zadajte:

INS [ESI], [DX]

ktorý má rovnaký účinok ako:

INS [EDI], [DX]

Programátor by mal vložiť dvojbajtovú adresu portu FFF0H do registra RDX:EDX:Dx a dvojbajtovú adresu C100H by mal vložiť do registra RSI:ESI alebo RDI:EDI. Pri spätnom prevode postupujte takto:

INS [DX], [ESI]

ktorý má rovnaký účinok ako:

INS [DX], [EDI]

6.37 Zásobník v x64

Rovnako ako procesor 6502, aj procesor x64 má zásobník v RAM. Zásobník pre x64 môže byť 2 16 = 65 536 bajtov alebo môže byť 2 32 = dĺžka 4 294 967 296 bajtov. Rastie aj smerom nadol. Keď sa obsah registra vloží do zásobníka, číslo v ukazovateli zásobníka RSP sa zníži o 8. Pamätajte, že adresa pamäte pre x64 je široká 64 bitov. Hodnota v ukazovateli zásobníka v µP ukazuje na ďalšie miesto v zásobníku v RAM. Keď sa obsah registra (alebo hodnota v jednom operande) presunie zo zásobníka do registra, číslo v ukazovateli zásobníka RSP sa zvýši o 8. Operačný systém určí veľkosť zásobníka a miesto jeho začiatku v RAM a rastie smerom nadol. Pamätajte, že stack je štruktúra Last-In-First-Out (LIFO), ktorá v tomto prípade rastie smerom nadol a zmenšuje sa smerom nahor.

Ak chcete preniesť obsah registra µP RBX do zásobníka, postupujte takto:

PUSH RBX

Ak chcete vrátiť poslednú položku v zásobníku späť do RBX, postupujte takto:

POP RBX

6.38 Postup v x64

Podprogram v x64 sa nazýva „procedúra“. Zásobník sa tu používa viac ako pre 6502 µP. Syntax procedúry x64 je:

názov_proc:

postupový orgán

…

správny

Skôr než budete pokračovať, všimnite si, že v operačných kódoch a návestiach pre podprogram x64 (všeobecné pokyny pre jazyk zostavy) sa nerozlišujú veľké a malé písmená. To znamená, že proc_name je rovnaký ako PROC_NAME. Rovnako ako 6502, názov procedúry (label) začína na začiatku nového riadku v textovom editore pre jazyk symbolických inštrukcií. Za ním nasleduje dvojbodka a nie medzera a operačný kód ako pri 6502. Nasleduje telo podprogramu, ktoré končí RET a nie RTS ako pri 6502 µP. Rovnako ako u 6502, každá inštrukcia v tele, vrátane RET, nezačína na začiatku svojho riadku. Upozorňujeme, že štítok tu môže mať viac ako 8 znakov. Ak chcete zavolať túto procedúru nad alebo pod zadanou procedúrou, postupujte takto:

CALL názov_proc

Pri 6502 je názov štítku len typ na volanie. Tu sa však napíše vyhradené slovo „CALL“ alebo „call“, za ktorým nasleduje po medzere názov procedúry (podprogramu).

Pri riešení procedúr sú zvyčajne dva postupy. Jedna procedúra volá druhú. Procedúra, ktorá volá (má inštrukciu volania), sa nazýva „volajúci“ a volaná procedúra sa nazýva „volaný“. Je potrebné dodržiavať konvenciu (pravidlá).

Pravidlá volajúceho

Volajúci by mal pri vyvolaní podprogramu dodržiavať nasledujúce pravidlá:

1. Pred volaním podprogramu by mal volajúci uložiť do zásobníka obsah určitých registrov, ktoré sú označené ako uložené pre volajúceho. Registre uložené pre volajúceho sú R10, R11 a všetky registre, do ktorých sa vkladajú parametre (RDI, RSI, RDX, RCX, R8, R9). Ak sa má obsah týchto registrov zachovať počas volania podprogramu, vložte ich do zásobníka namiesto uloženia do pamäte RAM. Tieto musia byť vykonané, pretože registre musí volaný použiť na vymazanie predchádzajúceho obsahu.

2. Ak je procedúrou napríklad pridanie dvoch čísel, tieto dve čísla sú parametre, ktoré sa majú odovzdať do zásobníka. Ak chcete parametre odovzdať podprogramu, vložte ich šesť do nasledujúcich registrov v poradí: RDI, RSI, RDX, RCX, R8, R9. Ak má podprogram viac ako šesť parametrov, posuňte zvyšok do zásobníka v opačnom poradí (t. j. posledný parameter ako prvý). Keďže zásobník rastie, prvý z dodatočných parametrov (skutočne siedmy parameter) je uložený na najnižšej adrese (táto inverzia parametrov sa historicky používala na to, aby funkcie (podprogramy) mohli byť odovzdané s premenlivým počtom parametrov).

3. Na zavolanie podprogramu (postupu) použite inštrukciu volania. Táto inštrukcia umiestni návratovú adresu na vrch parametrov zásobníka (najnižšia pozícia) a vetví kód podprogramu.

4. Po návrate podprogramu (t.j. bezprostredne po inštrukcii volania) musí volajúci zo zásobníka odstrániť všetky ďalšie parametre (okrem šiestich, ktoré sú uložené v registroch). Toto obnoví zásobník do stavu pred vykonaním hovoru.

5. Volajúci môže očakávať, že nájde návratovú hodnotu (adresu) podprogramu v registri RAX.

6. Volajúci obnoví obsah registrov uložených volajúcim (R10, R11 a všetky v registroch odovzdávajúcich parametre) ich vytiahnutím zo zásobníka. Volajúci môže predpokladať, že žiadne iné registre neboli zmenené podprogramom.

Vzhľadom na spôsob, akým je konvencia volania štruktúrovaná, sa zvyčajne stáva, že niektoré (alebo väčšina) z týchto krokov nevykonajú žiadne zmeny v zásobníku. Napríklad, ak existuje šesť alebo menej parametrov, v tomto kroku sa do zásobníka nič nevloží. Podobne programátori (a kompilátory) zvyčajne uchovávajú výsledky, o ktoré sa zaujímajú, mimo registrov uložených volajúcim v krokoch 1 a 6, aby zabránili nadmernému tlačeniu a vyskakovaniu.

Existujú dva ďalšie spôsoby odovzdania parametrov podprogramu, ale tým sa tento online kariérny kurz nebude zaoberať. Jeden z nich používa samotný zásobník namiesto všeobecných registrov.

Calleeho pravidlá

Definícia volaného podprogramu by mala dodržiavať nasledujúce pravidlá:

1. Prideľte lokálne premenné (premenné, ktoré sú vyvinuté v rámci procedúry) pomocou registrov alebo vytvorením miesta v zásobníku. Pripomeňme, že zásobník rastie smerom nadol. Takže, aby sa vytvoril priestor na vrchu zásobníka, ukazovateľ zásobníka by sa mal zmenšiť. Množstvo, o ktoré sa zníži ukazovateľ zásobníka, závisí od potrebného počtu lokálnych premenných. Napríklad, ak sa vyžaduje lokálny float a local long (celkom 12 bajtov), ukazovateľ zásobníka sa musí znížiť o 12, aby sa vytvoril priestor pre tieto lokálne premenné. V jazyku vysokej úrovne, ako je C, to znamená deklarovať premenné bez priradenia (inicializácie) hodnôt.

2. Ďalej sa musia uložiť hodnoty všetkých registrov, ktoré sú určené ako uložené volaného (všeobecné registre neuložené volajúcim), ktoré funkcia používa. Ak chcete uložiť registre, zatlačte ich na zásobník. Registre uložené pre volaného sú RBX, RBP a R12 až R15 (RSP je tiež zachovaný podľa konvencie hovorov, ale počas tohto kroku ho netreba tlačiť do zásobníka).

Po vykonaní týchto troch akcií môže samotná operácia podprogramu pokračovať. Keď je podprogram pripravený na návrat, pravidlá volania pokračujú.

3. Keď je podprogram hotový, návratová hodnota podprogramu by sa mala umiestniť do RAX, ak tam ešte nie je.

4. Podprogram musí obnoviť staré hodnoty všetkých registrov uložených volaným (RBX, RBP a R12 až R15), ktoré boli zmenené. Obsah registra sa obnoví jeho vybratím zo zásobníka. Všimnite si, že registre by sa mali otvárať v opačnom poradí, v akom boli stlačené.

5. Ďalej pridelíme lokálne premenné. Najjednoduchší spôsob, ako to urobiť, je pridať do RSP rovnakú sumu, ktorá bola odpočítaná v kroku 1.

6. Nakoniec sa vrátime k volajúcemu vykonaním inštrukcie ret. Táto inštrukcia nájde a odstráni príslušnú návratovú adresu zo zásobníka.

Príklad tela podprogramu volajúceho na volanie iného podprogramu, ktorý je „myFunc“, je nasledujúci (prečítajte si komentáre):

; Chcete zavolať funkciu „myFunc“, ktorá trvá tri

; celočíselný parameter. Prvý parameter je v RAX.

; Druhý parameter je konštanta 456. Tretí

; parameter je v pamäti 'variabl'

tlačiť rdi ; rdi bude param , tak si to ulož

; long retVal = myFunc (x, 456, z);

mov rdi , rax ; vložte prvý parameter do RDI

mov rsi, 456 ; vložte druhý parameter do RSI

mov rdx , [variabl] ; vložte tretí parameter do RDX

zavolajte myFunc; zavolajte funkciu

pop rdi ; obnoviť uloženú hodnotu RDI

; návratová hodnota myFunc je teraz dostupná v RAX

Príkladom funkcie volaného (myFunc) je (prečítajte si komentáre):

myFunc:

; ∗∗∗ Štandardný prológ podprogramu ∗∗∗

sub rsp, 8; priestor pre 64-bitovú lokálnu premennú (výsledok) pomocou „sub“ operačného kódu

push rbx ; uložiť volaného-uložiť registre

push rbp; obe bude používať myFunc

; ∗∗∗ Subrutina Telo ∗∗∗

mov rax , rdi ; parameter 1 na RAX

mov rbp , rsi ; parameter 2 na RBP

mov rbx, rdx; parameter 3 až rb x

mov [ rsp + 1 6 ] , rbx ; vložte rbx do lokálnej premennej

pridať [rsp + 16], rbp; pridajte rbp do lokálnej premennej

mov rax, [rsp +16]; mov obsah lokálnej premennej do RAX

; (návratná hodnota/konečný výsledok)

; ∗∗∗ Štandardný podprogramový epilóg ∗∗∗

pop rbp; obnoviť registre uloženia volaného

pop rbx ; naopak pri stlačení

pridať rsp, 8 ; uvoľniť lokálnu premennú (premenné). 8 znamená 8 bajtov

ret ; vyskočte najvyššiu hodnotu zo zásobníka, skočte tam

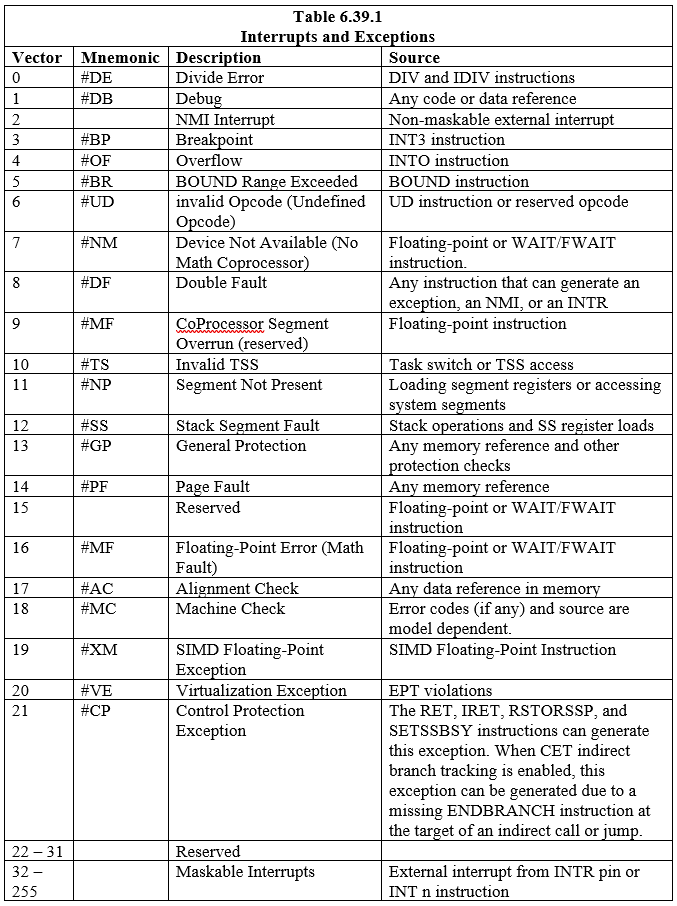

6.39 Prerušenia a výnimky pre x64

Procesor poskytuje dva mechanizmy na prerušenie vykonávania programu, prerušenia a výnimky:

- Prerušenie je asynchrónna (môže nastať kedykoľvek) udalosť, ktorú zvyčajne spúšťa I/O zariadenie.

- Výnimkou je synchrónna udalosť (vyskytuje sa pri vykonávaní kódu, predprogramovaní, na základe nejakého výskytu), ktorá sa generuje, keď procesor pri vykonávaní inštrukcie zistí jednu alebo viac preddefinovaných podmienok. Sú špecifikované tri triedy výnimiek: poruchy, pasce a prerušenia.

Procesor reaguje na prerušenia a výnimky v podstate rovnako. Keď je signalizované prerušenie alebo výnimka, procesor zastaví vykonávanie aktuálneho programu alebo úlohy a prepne sa na procedúru obsluhy, ktorá je napísaná špecificky na spracovanie stavu prerušenia alebo výnimky. Procesor pristupuje k procedúre obsluhy prostredníctvom záznamu v tabuľke deskriptorov prerušení (IDT). Keď obsluha dokončí spracovanie prerušenia alebo výnimky, riadenie programu sa vráti k prerušenému programu alebo úlohe.

Operačný systém, výkonné ovládače a/alebo ovládače zariadení bežne spracovávajú prerušenia a výnimky nezávisle od aplikačných programov alebo úloh. Aplikačné programy však môžu pristupovať k obslužným programom prerušenia a výnimiek, ktoré sú súčasťou operačného systému alebo ho vykonávajú prostredníctvom volaní v jazyku assembleru.

Je definovaných osemnásť (18) preddefinovaných prerušení a výnimiek, ktoré sú spojené so záznamami v IDT. Môže sa tiež vytvoriť a priradiť k tabuľke dvestodvadsaťštyri (224) prerušení definovaných používateľom. Každé prerušenie a výnimka v IDT je identifikovaná číslom, ktoré sa nazýva „vektor“. Tabuľka 6.39.1 uvádza prerušenia a výnimky so záznamami v IDT a ich príslušnými vektormi. Vektory 0 až 8, 10 až 14 a 16 až 19 sú preddefinované prerušenia a výnimky. Vektory 32 až 255 sú pre softvérovo definované prerušenia (užívateľské), ktoré sú buď pre softvérové prerušenia alebo maskovateľné hardvérové prerušenia.

Keď procesor zistí prerušenie alebo výnimku, vykoná jednu z nasledujúcich vecí:

- Vykonajte implicitné volanie procedúry handlera

- Vykonajte implicitné volanie úlohy obsluhy

6.4 Základy 64-bitovej počítačovej architektúry ARM

Architektúry ARM definujú rodinu RISC procesorov, ktoré sú vhodné na použitie v širokej škále aplikácií. ARM je architektúra načítania/ukladania, ktorá vyžaduje, aby sa údaje načítali z pamäte do registra predtým, ako sa s ňou môže uskutočniť akékoľvek spracovanie, ako napríklad operácia ALU (Arithmetic Logic Unit). Následná inštrukcia uloží výsledok späť do pamäte. Aj keď sa to môže zdať ako krok späť od architektúr x86 a x64, ktoré operujú priamo s operandami v pamäti v jedinej inštrukcii (samozrejme s použitím registrov procesora), prístup načítanie/ukladanie v praxi umožňuje niekoľko sekvenčných operácií. vykonávať pri vysokej rýchlosti na operande po jeho načítaní do jedného z mnohých registrov procesora. Procesory ARM majú možnosť malej endianity alebo big-endianness. Predvolené nastavenie ARM 64 je little-endian, čo je konfigurácia, ktorú bežne používajú operačné systémy. 64-bitová architektúra ARM je moderná a má nahradiť 32-bitovú architektúru ARM.

Poznámka : Každá inštrukcia pre 64-bitový ARM µP je dlhá 4 bajty (32 bitov).

6.41 Sada 64-bitových registrov ARM

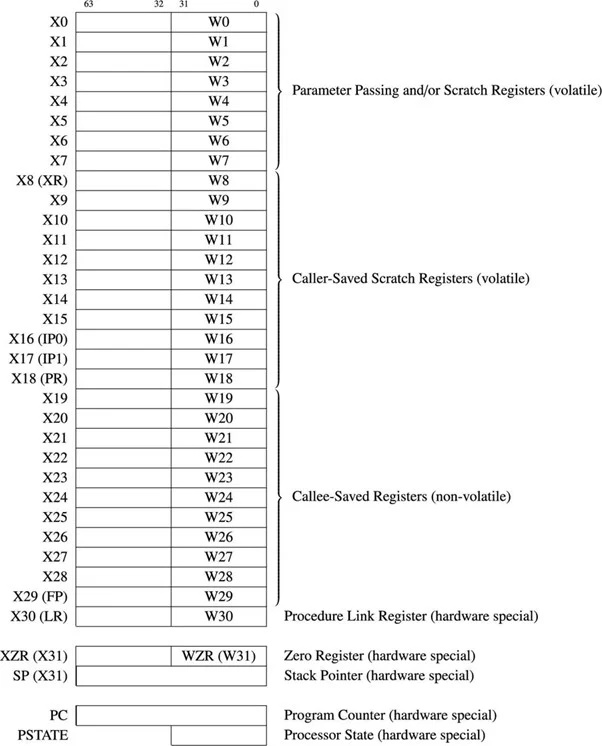

Existuje 31 všeobecných 64-bitových registrov pre 64-bitový ARM µP. Nasledujúci diagram zobrazuje univerzálne registre a niektoré dôležité registre:

Obr.4.11.1 64-bitový všeobecný účel a niektoré dôležité registre

Univerzálne registre sa označujú ako X0 až X30. Prvá 32-bitová časť pre každý register sa označuje ako W0 až W30. Ak nie je zdôraznený rozdiel medzi 32 a 64 bitmi, použije sa predpona „R“. Napríklad R14 označuje W14 alebo X14.

6502 µP má 16-bitové počítadlo programov a dokáže adresovať 2 16 miesta bajtov pamäte. 64-bitový ARM µP má 64-bitové počítadlo programov a môže adresovať až 2 64 = 1,844674407 x 1019 (v skutočnosti 18 446 744 073 709 551 616) miest bajtov pamäte. Počítadlo programu obsahuje adresu nasledujúcej inštrukcie, ktorá sa má vykonať. Dĺžka inštrukcie ARM64 alebo AArch64 je zvyčajne štyri bajty. Procesor automaticky zvýši tento register o štyri po načítaní každej inštrukcie z pamäte.

Register Stack Pointer alebo SP nepatrí medzi 31 všeobecných registrov. Ukazovateľ zásobníka akejkoľvek architektúry ukazuje na posledný záznam zásobníka v pamäti. Pre ARM-64 zásobník rastie smerom nadol.

6502 µP má 8-bitový stavový register procesora. Ekvivalent v ARM64 sa nazýva register PSTATE. V tomto registri sú uložené príznaky, ktoré sa používajú na výsledky operácií a na riadenie procesora (µP). Má šírku 32 bitov. Nasledujúca tabuľka uvádza názvy, index a významy bežne používaných bitov v registri PSTATE:

| Tabuľka 6.41.1 Najpoužívanejšie príznaky PSTATE (bity) |

||

|---|---|---|

| Symbol | Trocha | Účel |

| M | 0-3 | Režim: Aktuálna úroveň oprávnení na spustenie (USR, SVC atď.). |

| T | 4 | Thumb: Nastavuje sa, ak je aktívna inštrukčná sada T32 (Thumb). Ak nie je začiarknuté, súprava inštrukcií ARM je aktívna. Používateľský kód môže tento bit nastaviť a vymazať. |

| A | 9 | Endianness: Nastavenie tohto bitu aktivuje režim big-endian. Ak je jasné, režim little-endian je aktívny. Predvolený je režim little-endian. |

| Q | 27 | Príznak kumulatívnej saturácie: Nastavuje sa, ak v určitom bode série operácií dôjde k pretečeniu alebo saturácii |

| V | 28 | Príznak pretečenia: Nastavuje sa, ak operácia viedla k podpísanému pretečeniu. |

| C | 29 | Príznak prenosu: Označuje, či pridanie spôsobilo prenos alebo odčítanie spôsobilo vypožičanie. |

| S | 30 | Príznak nuly: Nastaví sa, ak je výsledok operácie nula. |

| N | 31 | Negatívny príznak: Nastavuje sa, ak je výsledok operácie negatívny. |

ARM-64 µP má mnoho ďalších registrov.

SIMD

SIMD znamená Single Instruction, Multiple Data. To znamená, že jedna inštrukcia v jazyku symbolických inštrukcií môže pôsobiť na viacero údajov súčasne v jednom mikroprocesore. Existuje tridsaťdva registrov so šírkou 128 bitov na použitie s operáciami SIMD a s pohyblivou rádovou čiarkou.

6.42 Mapovanie pamäte

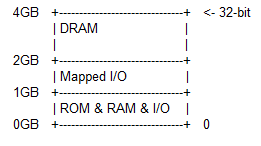

RAM aj DRAM sú pamäte s náhodným prístupom. DRAM funguje pomalšie ako RAM. DRAM je lacnejšia ako RAM. Ak je v pamäti viac ako 32 gigabajtov (GB) pokračujúcej DRAM, vyskytnú sa ďalšie problémy so správou pamäte: 32 GB = 32 x 1024 x 1024 x 1024 bajtov. Pre celý pamäťový priestor, ktorý je oveľa väčší ako 32 GB, by sa mala DRAM nad 32 GB prelínať s RAM pre lepšiu správu pamäte. Aby ste porozumeli mape pamäte ARM-64, mali by ste najprv porozumieť mape pamäte 4 GB pre 32-bitovú centrálnu procesorovú jednotku ARM (CPU). CPU znamená µP. Pre 32-bitový počítač je maximálny adresovateľný priestor pamäte 2 32 = 4 x 2 10 x 2 10 x 2 10 = 4 x 1024 x 1024 x 1024 = 4 294 967 296 = 4 GB.

32-bitová mapa pamäte ARM

Pamäťová mapa pre 32-bitový ARM je:

Pre 32-bitový počítač je maximálna veľkosť celej pamäte 4 GB. Od adresy 0 GB po adresu 1 GB sú umiestnenie operačného systému ROM, RAM a I/O. Celá myšlienka ROM OS, RAM a I/O adries je podobná situácii Commodore-64 s možným 6502 CPU. OS ROM pre Commodore-64 je na hornom konci pamäťového priestoru. Operačný systém ROM je tu oveľa väčší ako operačný systém Commodore-64 a je na začiatku celého adresného priestoru pamäte. V porovnaní s inými modernými počítačmi je tu ROM OS kompletný v tom zmysle, že je porovnateľný s množstvom OS na ich pevných diskoch. Existujú dva hlavné dôvody, prečo mať OS v integrovaných obvodoch ROM: 1) CPU ARM sa väčšinou používajú v malých zariadeniach, ako sú smartfóny. Mnohé pevné disky sú väčšie ako smartfóny a iné malé zariadenia, 2) kvôli bezpečnosti. Keď je OS v pamäti Iba na čítanie, nemôže byť poškodený (časti prepísané) hackermi. Sekcie RAM a vstupno-výstupné sekcie sú tiež veľmi veľké v porovnaní s sekciami Commodore-64.

Keď sa zapne napájanie s 32-bitovým operačným systémom ROM, operačný systém musí začať (zaviesť z) na adrese 0x00000000 alebo na adrese 0xFFFF0000, ak je povolený systém HiVEC. Takže, keď sa po fáze resetovania zapne napájanie, hardvér CPU načíta 0x00000000 alebo 0xFFFF0000 do počítadla programov. Predpona „0x“ znamená Hexadecimálne. Zavádzacia adresa ARMv8 64bit CPU je definovaná implementácia. Autor však počítačovému inžinierovi radí, aby začal na 0x00000000 alebo 0xFFFF0000 kvôli spätnej kompatibilite.

Od 1 GB do 2 GB je mapovaný vstup/výstup. Existuje rozdiel medzi mapovaným I/O a iba I/O, ktoré sa nachádzajú medzi 0 GB a 1 GB. Pri I/O je adresa pre každý port pevná ako pri Commodore-64. Pri mapovanom I/O nemusí byť adresa každého portu nevyhnutne rovnaká pre každú operáciu počítača (dynamická).

Od 2 GB do 4 GB je DRAM. Toto je očakávaná (alebo obvyklá) RAM. DRAM je skratka pre Dynamic RAM, nie je to zmysel meniacej sa adresy počas prevádzky počítača, ale v tom zmysle, že hodnota každej bunky vo fyzickej RAM sa musí obnovovať pri každom hodinovom impulze.

Poznámka :

- Od 0x0000,0000 do 0x0000, FFFF je OS ROM.

- Od 0x0001,0000 do 0x3FFF,FFFF môže byť viac ROM, potom RAM a potom nejaké I/O.

- Od 0x4000,0000 do 0x7FFF,FFFF sú povolené ďalšie I/O a/alebo mapované I/O.

- Od 0x8000,0000 do 0xFFFF, FFFF je očakávaná DRAM.

To znamená, že očakávaná DRAM nemusí v praxi začínať na hranici 2 GB pamäte. Prečo by mal programátor rešpektovať ideálne hranice, keď na základnej doske nie je dostatok fyzických RAM bánk? Je to preto, že zákazník nemá dostatok peňazí pre všetky banky RAM.

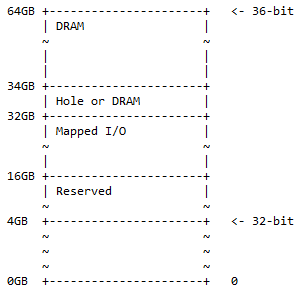

36-bitová mapa pamäte ARM

V prípade 64-bitového počítača ARM sa všetkých 32 bitov používa na adresovanie celej pamäte. V prípade 64-bitového počítača ARM možno prvých 36 bitov použiť na adresovanie celej pamäte, čo je v tomto prípade 2 36 = 68 719 476 736 = 64 GB. Toto je už veľa pamäte. Bežné počítače dnes takéto množstvo pamäte nepotrebujú. Toto ešte nedosahuje maximálny rozsah pamäte, ku ktorej je možné pristupovať pomocou 64 bitov. Mapa pamäte pre 36-bitový procesor ARM je:

Od adresy 0 GB po adresu 4 GB je 32-bitová pamäťová mapa. „Vyhradené“ znamená, že sa nepoužíva a uchováva sa pre budúce použitie. Nemusia to byť fyzické pamäťové banky, ktoré sú pre tento priestor zasunuté na základnej doske. DRAM a mapované I/O tu majú rovnaký význam ako pre 32-bitovú pamäťovú mapu.

V praxi sa môže vyskytnúť nasledujúca situácia:

- 0x1 0000 0000 – 0x3 FFFF FFFF; rezervované. 12 GB adresového priestoru je vyhradených pre budúce použitie.

- 0x4 0000 0000 – 0x7 FFFF FFFF; mapované I/O. Pre dynamicky mapované I/O je k dispozícii 16 GB adresového priestoru.

- 0x8 0000 0000 – 0x8 7FFF FFFF FFFF; Diera alebo DRAM. 2 GB adresného priestoru môže obsahovať jedno z nasledujúcich:

- Otvor na umožnenie rozdelenia zariadenia DRAM na oddiely (ako je popísané v nasledujúcej diskusii).

- DRAM.

- 0x8 8000 0000 – 0xF FFFF FFFF; DRAM. 30 GB adresného priestoru pre DRAM.

Táto pamäťová mapa je nadmnožinou 32-bitovej mapy adries, pričom dodatočný priestor je rozdelený ako 50 % DRAM (1/2) s voliteľným otvorom a 25 % mapovaného I/O priestoru a rezervovaného priestoru (1/4 ). Zvyšných 25 % (1/4) je pre 32-bitovú pamäťovú mapu ½ + ¼ + ¼ = 1.

Poznámka : Od 32 bitov do 360 bitov je pridanie 4 bitov k najvýznamnejšej strane 36 bitov.

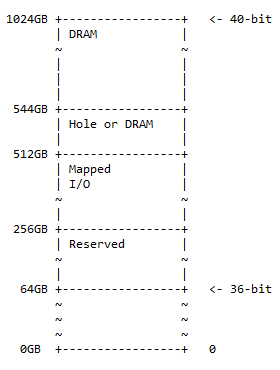

40-bitová mapa pamäte

40-bitová mapa adries je nadmnožinou 36-bitovej mapy adries a sleduje rovnaký vzor 50 % DRAM s voliteľnou dierou v nej, 25 % mapovaného I/O priestoru a rezervovaného priestoru a zvyšných 25 % priestor pre predchádzajúcu pamäťovú mapu (36-bit). Diagram pre pamäťovú mapu je:

Veľkosť otvoru je 544 – 512 = 32 GB. V praxi sa môže vyskytnúť nasledujúca situácia:

- 0x10 0000 0000 – 0x3F FFFF FFFF; rezervované. 192 GB adresového priestoru je vyhradených pre budúce použitie.

- 0x40 0000 0000 – 0x7F FFFF FFFF; zmapované. I/O Pre dynamicky mapované I/O je k dispozícii 256 GB adresného priestoru.

- 0x80 0000 0000 – 0x87 FFFF FFFF; otvor alebo DRAM. 32 GB adresného priestoru môže obsahovať jedno z nasledujúcich:

- Otvor na umožnenie rozdelenia zariadenia DRAM (ako je popísané v nasledujúcej diskusii)

- DRAM

- 0x88 0000 0000 – 0xFF FFFF FFFF; DRAM. 480 GB adresového priestoru pre DRAM.

Poznámka : Od 36 bitov do 40 bitov je pridanie 4 bitov k najvýznamnejšej strane 36 bitov.

DRAM Diera

V pamäťovej mape nad 32-bitmi je to buď diera DRAM alebo pokračovanie DRAM zhora. Keď je to diera, treba to oceniť takto: Diera DRAM poskytuje spôsob, ako rozdeliť veľké zariadenie DRAM do viacerých rozsahov adries. Voliteľný otvor DRAM sa navrhuje na začiatku vyššej hranice adresy DRAM. To umožňuje zjednodušenú schému dekódovania pri rozdeľovaní veľkokapacitného zariadenia DRAM cez nižšiu fyzicky adresovanú oblasť.

Napríklad časť 64 GB DRAM je rozdelená do troch oblastí s posunmi adries vykonanými jednoduchým odčítaním bitov adries vyššieho rádu takto:

| Tabuľka 6.42.1 Príklad rozdelenia 64 GB DRAM s otvormi |

|||

|---|---|---|---|

| Fyzické adresy v SoC | Offset | Interná adresa DRAM | |

| 2 GB (32-bitová mapa) | 0x00 8000 0000 – 0x00 FFFF FFFF | -0x00 8000 0000 | 0x00 0000 0000 – 0x00 7FFF FFFF |

| 30 GB (36-bitová mapa) | 0x08 8000 0000 – 0x0F FFFF FFFF | -0x08 0000 0000 | 0x00 8000 0000 – 0x07 FFFF FFFF |

| 32 GB (40-bitová mapa) | 0x88 0000 0000 – 0x8F FFFF FFFF | -0x80 000 0000 | 0x08 0000 0000 – 0x0F FFFF FFFF |

Navrhované 44-bitové a 48-bitové mapy adresovanej pamäte pre procesory ARM

Predpokladajme, že osobný počítač má 1024 GB (= 1 TB) pamäte; to je príliš veľa pamäte. A tak 44-bitové a 48-bitové adresované pamäťové mapy pre ARM CPU pre 16 TB a 256 TB sú len návrhy pre budúce počítačové potreby. V skutočnosti tieto návrhy pre CPU ARM sledujú rovnaké rozdelenie pamäte podľa pomeru ako predchádzajúce pamäťové mapy. To znamená: 50 % DRAM s voliteľným otvorom v nej, 25 % mapovaného I/O priestoru a rezervovaného priestoru a zvyšných 25 % priestoru pre predchádzajúcu pamäťovú mapu.

52-bitové, 56-bitové, 60-bitové a 64-bitové adresované pamäťové mapy sa ešte majú navrhnúť pre 64-bitové ARM pre ďalekú budúcnosť. Ak vedci v tom čase stále považujú rozdelenie celého pamäťového priestoru 50 : 25 : 25 za užitočné, pomer zachovajú.

Poznámka : SoC znamená System-on-Chip, čo sa týka obvodov v čipe µP, ktoré by tam inak neboli.

SRAM alebo statická pamäť s náhodným prístupom je rýchlejšia ako tradičnejšia DRAM, ale vyžaduje väčšiu plochu kremíka. SRAM nevyžaduje obnovenie. RAM si čitateľ môže predstaviť ako SRAM.

6.43 Režimy adresovania v assembleri pre ARM 64

ARM je architektúra načítania/ukladania, ktorá vyžaduje, aby sa údaje načítali z pamäte do registra procesora predtým, ako sa s ňou môže uskutočniť akékoľvek spracovanie, ako napríklad aritmetická logická operácia. Následná inštrukcia uloží výsledok späť do pamäte. Aj keď sa to môže zdať ako krok späť od architektúry x86 a jej nasledujúcich architektúr x64, ktoré pracujú priamo s operandami v pamäti v jedinej inštrukcii, v praxi prístup načítania/ukladania umožňuje vykonať niekoľko sekvenčných operácií vysokou rýchlosťou na operand po jeho načítaní do jedného z mnohých registrov procesora.

Formát montážneho jazyka ARM má podobnosti a rozdiely so sériou x64 (x86).

- Offset : Do základného registra možno pridať konštantu so znamienkom. Offset je napísaný ako súčasť inštrukcie. Napríklad: ldr x0, [rx, #10] načíta r0 so slovom na adrese r1+10.

- Registrovať : Prírastok bez znamienka, ktorý je uložený v registri, možno pridať alebo odpočítať od hodnoty v základnom registri. Napríklad: ldr r0, [x1, x2] načíta r0 so slovom na adrese x1+x2. Ktorýkoľvek z registrov možno považovať za základný register.

- Zmenšený register : Prírastok v registri je posunutý doľava alebo doprava o určený počet bitových pozícií pred pridaním alebo odčítaním od základnej hodnoty registra. Napríklad: ldr x0, [x1, x2, lsl #3] načíta r0 so slovom na adrese r1+(r2×8). Posun môže byť logický posun doľava alebo doprava (lsl alebo lsr), ktorý vkladá nulové bity do uvoľnených bitových pozícií, alebo aritmetický posun doprava (asr), ktorý replikuje znamienkový bit na uvoľnené pozície.

Keď sú zahrnuté dva operandy, cieľ sa nachádza pred (vľavo) pred zdrojom (existujú určité výnimky). Operačné kódy pre jazyk assembleru ARM nerozlišujú veľké a malé písmená.

Okamžitý režim adresovania ARM64

Príklad:

mov r0, #0xFF000000 ; Nahrajte 32-bitovú hodnotu FF000000h do r0

Desatinná hodnota je bez 0x, ale stále pred ňou stojí #.

Zaregistrujte sa priamo

Príklad:

mov x0, x1; Skopírujte x1 do x0

Registrovať Nepriame

Príklad:

str x0, [x3] ; Uložte x0 na adresu v x3

Zaregistrujte nepriame s posunom

Príklady:

ldr x0, [x1, #32] ; Načítaj r0 hodnotou na adrese [r1+32]; r1 je základný register

str x0, [x1, #4] ; Uložte r0 na adresu [r1+4]; r1 je základný register; čísla sú základ 10

Registrovať nepriame s posunom (vopred navýšené)

Príklady:

ldr x0, [x1, #32]! ; Načítajte r0 pomocou [r1+32] a aktualizujte r1 na (r1+32)

str x0, [x1, #4]! ; Uložte r0 na [r1+4] a aktualizujte r1 na (r1+4)

Všimnite si použitie „!“ symbol.

Registrovať nepriame s posunom (po zvýšení)

Príklady:

ldr x0, [x1], #32 ; Načítať [x1] na x0, potom aktualizovať x1 na (x1+32)

str x0, [x1], #4 ; Uložte x0 na [x1], potom aktualizujte x1 na (x1+4)

Dvojitý register nepriamy

Adresa operandu je súčtom základného registra a prírastkového registra. Názvy registrov sú ohraničené hranatými zátvorkami.

Príklady:

ldr x0, [x1, x2]; Načítať x0 pomocou [x1+x2]

str x0, [rx, x2]; Uložiť x0 až [x1+x2]

Režim relatívneho adresovania

V režime relatívneho adresovania je účinnou inštrukciou nasledujúca inštrukcia v počítadle programov plus index. Index môže byť kladný alebo záporný.

Príklad:

ldr x0, [pc, #24]

To znamená register záťaže X0 so slovom, na ktoré ukazuje obsah PC plus 24.

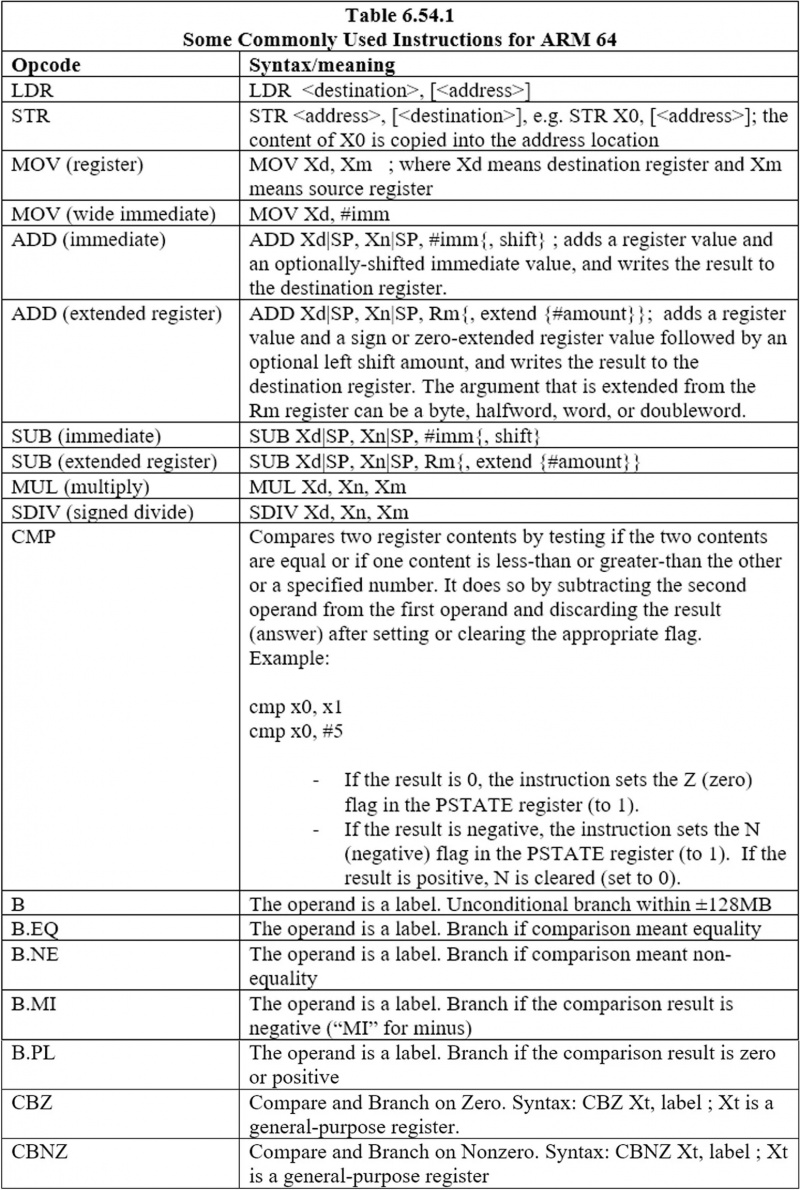

6.44 Niektoré bežne používané pokyny pre ARM 64

Tu sú bežne používané pokyny:

6.45 Slučovanie

Ilustračné

Nasledujúci kód neustále pridáva hodnotu v registri X10 k hodnote v X9, kým hodnota v X8 nebude nula. Predpokladajme, že všetky hodnoty sú celé čísla. Hodnota v X8 sa odpočíta o 1 v každej iterácii:

slučka:

CBZ X8, preskočiť

PRIDAŤ X9, X9, X10; prvý X9 je cieľ a druhý X9 je zdroj

SUB X8, X8, #1; prvý X8 je cieľ a druhý X8 je zdroj

B slučka

preskočiť:

Podobne ako pri 6502 µP a X64 µP začína označenie v ARM 64 µP na začiatku riadku. Zvyšok pokynov začína na niektorých miestach za začiatkom riadku. Pri x64 a ARM 64 za štítkom nasleduje dvojbodka a nový riadok. Zatiaľ čo pri 6502 nasleduje po označení pokyn za medzerou. V predchádzajúcom kóde prvá inštrukcia, ktorá je „CBZ X8, skip“, znamená, že ak je hodnota v X8 nula, pokračujte na štítku „skip:“, preskočte pokyny medzi tým a pokračujte zvyškom pokynov nižšie. „preskočiť:“. „Slučka B“ je bezpodmienečný skok na označenie „slučka“. Namiesto „slučky“ možno použiť akýkoľvek iný názov štítku.

Takže, podobne ako pri 6502 µP, použite pokyny na vetvenie, aby ste mali slučku s ARM 64.

6.46 ARM 64 Vstup/Výstup

Všetky periférie ARM (interné porty) sú namapované na pamäť. To znamená, že programovacie rozhranie je množina pamäťovo adresovaných registrov (interných portov). Adresa takéhoto registra je offsetom od špecifickej základnej adresy pamäte. Je to podobné tomu, ako 6502 robí vstup/výstup. ARM nemá možnosť samostatného I/O adresného priestoru.

6.47 Zásobník ARM 64

ARM 64 má zásobník v pamäti (RAM) podobným spôsobom ako 6502 a x64. Avšak, s ARM64, neexistuje žiadny push alebo pop operačný kód. Zásobník v ARM 64 tiež rastie smerom nadol. Adresa v ukazovateli zásobníka ukazuje hneď za posledný bajt poslednej hodnoty, ktorá je umiestnená v zásobníku.

Dôvod, prečo pre ARM64 neexistuje žiadny generický pop alebo push operačný kód, je ten, že ARM 64 spravuje svoj zásobník v skupinách po sebe nasledujúcich 16 bajtov. Hodnoty však existujú v bajtových skupinách jeden bajt, dva bajty, štyri bajty a 8 bajtov. Takže jedna hodnota môže byť umiestnená do zásobníka a ostatné miesta (umiestnenia bajtov), ktoré tvoria 16 bajtov, sú vyplnené fiktívnymi bajtmi. To má nevýhodu v plytvaní pamäťou. Lepším riešením je vyplniť 16-bajtové miesto menšími hodnotami a nechať si napísať nejaký programátorský kód, ktorý sleduje, odkiaľ hodnoty v 16-bajtovom umiestnení pochádzajú (registruje). Tento dodatočný kód je potrebný aj pri sťahovaní hodnôt. Alternatívou k tomu je vyplniť dva 8-bajtové všeobecné registre rôznymi hodnotami a potom odoslať obsah dvoch 8-bajtových registrov do zásobníka. Tu je stále potrebný ďalší kód na sledovanie špecifických malých hodnôt, ktoré idú do zásobníka a opúšťajú zásobník.

Nasledujúci kód ukladá štyri 4-bajtové údaje do zásobníka:

str w0, [sp, #-4]!

str w1, [sp, #-8]!

str w2, [sp, #-12]!

str w3, [sp, #-16]!

Prvé štyri bajty (w) registrov – x0, x1, x2 a x3 – sa odošlú na 16-po sebe idúce bajtové miesta v zásobníku. Všimnite si použitie „str“ a nie „push“. Všimnite si symbol výkričníka na konci každého pokynu. Keďže zásobník pamäte rastie smerom nadol, prvá štvorbajtová hodnota začína na pozícii, ktorá je mínus štyri bajty pod predchádzajúcim ukazovateľom zásobníka. Zostávajúce štvorbajtové hodnoty nasledujú, idú dole. Nasledujúci segment kódu urobí správny (a v poradí) ekvivalent presunutia štyroch bajtov:

ldr w3, [sp], #0

ldr w2, [sp], #4

ldr w1, [sp], #8

ldr w0, [sp], #12

Všimnite si použitie operačného kódu ldr namiesto pop. Upozorňujeme tiež, že sa tu nepoužíva výkričník.

Všetky bajty v X0 (8 bajtov) a X1 (8 bajtov) možno odoslať do 16 bajtového umiestnenia v zásobníku nasledovne:

stp x0, x1, [sp, #-16]! ; 8 + 8 = 16

V tomto prípade nie sú potrebné registre x2 (w2) a x3 (w3). Všetky požadované bajty sú v registroch X0 a X2. Všimnite si operačný kód stp na ukladanie párov obsahu registra do pamäte RAM. Všimnite si aj symbol výkričníka. Popový ekvivalent je:

ldp x0, x1, [sp], #0

Pre tento pokyn nie je žiadny výkričník. Všimnite si operačný kód LDP namiesto LDR pre načítanie dvoch po sebe idúcich dátových umiestnení z pamäte do dvoch µP registrov. Pamätajte tiež, že kopírovanie z pamäte do registra µP sa načítava, nezamieňajte si to s načítaním súboru z disku do pamäte RAM a kopírovanie z registra µP do pamäte RAM je ukladaním.

6.48 Podprogram

Podprogram je blok kódu, ktorý vykonáva úlohu, voliteľne na základe niektorých argumentov a voliteľne vracia výsledok. Podľa konvencie sa registre R0 až R3 (štyri registre) používajú na odovzdanie argumentov (parametrov) podprogramu a R0 sa používa na odovzdanie výsledku späť volajúcemu. Podprogram, ktorý potrebuje viac ako 4 vstupy, používa zásobník pre ďalšie vstupy. Ak chcete zavolať podprogram, použite odkaz alebo inštrukciu podmienenej vetvy. Syntax pre inštrukciu prepojenia je:

BL štítok

Kde BL je operačný kód a označenie predstavuje začiatok (adresu) podprogramu. Táto vetva je bezpodmienečná, vpred alebo vzad do 128 MB. Syntax pre inštrukciu podmieneného vetvenia je:

B.cond štítok

Kde cond je podmienka, napr. eq (rovná sa) alebo ne (nerovná sa). Nasledujúci program má podprogram doadd, ktorý pridáva hodnoty dvoch argumentov a vracia výsledok v R0:

AREA subrout, CODE, READONLEN ; Pomenujte tento blok kódu

VSTUP ; Označte prvý pokyn na vykonanie

štart MOV r0, #10 ; Nastavte parametre

MOV r1, #3

BL doadd ; Volanie podprogramu

stop MOV r0, #0x18 ; angel_SWIreason_ReportException

LDR r1, =0x20026 ; ADP_Stopped_ApplicationExit

SVC #0x123456 ; ARM semihosting (predtým SWI)

doadd ADD r0, r0, r1 ; Kód podprogramu

BX lr ; Návrat z podprogramu

;

KONIEC ; Označte koniec súboru

Čísla, ktoré sa majú pridať, sú desiatkové 10 a 3. Prvé dva riadky v tomto bloku kódu (programu) budú vysvetlené neskôr. Nasledujúce tri riadky posielajú 10 do registra R0 a 3 do registra R1 a tiež volajú podprogram doadd. „doadd“ je označenie, ktoré obsahuje adresu začiatku podprogramu.

Podprogram pozostáva len z dvoch riadkov. Prvý riadok pridáva obsah 3 R k obsahu 10 R0, čo umožňuje výsledok 13 v R0. Druhý riadok s operačným kódom BX a operandom LR sa vráti z podprogramu do kódu volajúceho.

SPRÁVNY

Operačný kód RET v ARM 64 stále pracuje s podprogramom, ale funguje inak ako RTS v 6502 alebo RET na x64, alebo kombinácia „BX LR“ v ARM 64. V ARM 64 je syntax pre RET:

ROVNO {Xn}

Táto inštrukcia dáva programu možnosť pokračovať s podprogramom, ktorý nie je volajúcim podprogramom, alebo len pokračovať s nejakou inou inštrukciou a jej nasledujúcim segmentom kódu. Xn je všeobecný register, ktorý obsahuje adresu, na ktorú má program pokračovať. Tento pokyn sa bezpodmienečne rozvetvuje. Ak nie je zadané Xn, štandardne sa použije obsah X30.

Štandardné volanie procedúry

Ak programátor chce, aby jeho kód interagoval s kódom, ktorý je napísaný niekým iným, alebo s kódom vytvoreným kompilátorom, musí sa programátor dohodnúť s osobou alebo autorom kompilátora na pravidlách používania registra. Pre architektúru ARM sa tieto pravidlá nazývajú Standard Call Standard alebo PCS. Ide o dohody medzi dvoma alebo tromi stranami. PCS špecifikuje nasledovné:

- Ktoré µP registre sa používajú na odovzdanie argumentov do funkcie (podprogramu)

- Ktoré µP registre sa používajú na vrátenie výsledku funkcii, ktorá volá, ktorá je známa ako volajúci

- Ktorý µP zaregistruje funkciu, ktorá je volaná a ktorá je známa ako volaný, sa môže poškodiť

- Ktorý µP zaregistruje volaného, nemôže sa poškodiť

6.49 Prerušenia

Pre procesor ARM sú k dispozícii dva typy obvodov radiča prerušení:

- Štandardný radič prerušení: Obslužný program prerušení určuje, ktoré zariadenie vyžaduje servis, načítaním bitmapového registra zariadenia v radiči prerušení.

- Vector Interrupt Controller (VIC): Uprednostňuje prerušenia a zjednodušuje určenie, ktoré zariadenie spôsobilo prerušenie. Po priradení priority a adresy obsluhy každému prerušeniu VIC odovzdá procesoru signál prerušenia iba vtedy, ak je priorita nového prerušenia vyššia ako priorita aktuálne vykonávanej obsluhy prerušenia.

Poznámka : Výnimka sa týka chyby. Podrobnosti o radiči vektorových prerušení pre 32-bitový počítač ARM sú nasledovné (64-bitový je podobný):

| Tabuľka 6.49.1 Výnimka/prerušenie vektora ARM pre 32-bitový počítač |

|||

|---|---|---|---|

| Výnimka/Prerušenie | Krátka ruka | Adresa | Vysoká adresa |

| Resetovať | RESETOVAŤ | 0x00000000 | 0xffff0000 |

| Nedefinovaný pokyn | UNDEF | 0x00000004 | 0xffff0004 |

| Softvérové prerušenie | SWI | 0x00000008 | 0xffff0008 |

| Prerušenie predbežného načítania | pabt | 0x0000000C | 0xffff000C |

| Dátum potratu | DABT | 0x00000010 | 0xffff0010 |

| Rezervované | – | 0x00000014 | 0xffff0014 |

| Žiadosť o prerušenie | IRQ | 0x00000018 | 0xffff0018 |

| Požiadavka na rýchle prerušenie | FIQ | 0x0000001C | 0xffff001C |

Toto vyzerá ako usporiadanie pre architektúru 6502, kde NMI , BR , a IRQ môžu mať ukazovatele na stránke nula a zodpovedajúce rutiny sú vysoko v pamäti (ROM OS). Stručné popisy riadkov predchádzajúcej tabuľky sú nasledovné:

RESETOVAŤ

Stáva sa to pri zapnutí procesora. Inicializuje systém a nastavuje zásobníky pre rôzne režimy procesora. Je to výnimka s najvyššou prioritou. Po vstupe do obsluhy resetovania je CPSR v režime SVC a bity IRQ aj FIQ sú nastavené na 1, čím sa maskujú akékoľvek prerušenia.

DÁTUM POTRATU

Druhá najvyššia priorita. Stáva sa to, keď sa pokúšame čítať/zapisovať na neplatnú adresu alebo získať nesprávne prístupové oprávnenie. Po vstupe do Data Abort Handler budú IRQ deaktivované (I-bit set 1) a FIQ bude aktivované. IRQ sú maskované, ale FIQ zostávajú nezamaskované.

FIQ

Prerušenie s najvyššou prioritou, IRQ a FIQ, sú vypnuté, kým sa nespracuje FIQ.

IRQ

Prerušenie s vysokou prioritou, obslužný program IRQ, sa zadáva iba vtedy, ak neprebieha žiadne prerušenie FIQ a dát.

Pre-Fetch Abort

Je to podobné ako pri prerušení údajov, ale stane sa to pri zlyhaní načítania adresy. Po vstupe do obslužného programu sú IRQ deaktivované, ale FIQ zostanú povolené a môžu sa vyskytnúť počas prerušenia predbežného načítania.

SWI

Výnimka softvérového prerušenia (SWI) nastane, keď sa vykoná inštrukcia SWI a žiadna z iných výnimiek s vyššou prioritou nebola označená.

Nedefinovaný pokyn

Výnimka Undefined Instruction nastane, keď inštrukcia, ktorá nie je v inštrukčnej sade ARM alebo Thumb, dosiahne štádium vykonania pipeline a žiadna z ostatných výnimiek nebola označená príznakom. Toto je rovnaká priorita ako SWI, ktorá sa môže stať naraz. To znamená, že inštrukcia, ktorá sa vykonáva, nemôže byť súčasne inštrukciou SWI aj nedefinovanou inštrukciou.

ARM Spracovanie výnimiek

Nasledujúce udalosti nastanú, keď nastane výnimka:

- Uložte CPSR do SPSR režimu výnimky.

- PC je uložené v LR režimu výnimky.

- Linkový register je nastavený na konkrétnu adresu na základe aktuálnej inštrukcie. Napríklad: pre ISR, LR = posledná vykonaná inštrukcia + 8.

- Aktualizujte CPSR o výnimke.

- Nastavte počítač na adresu obsluhy výnimky.

6.5 Pokyny a údaje

Údaje sa týkajú premenných (označenia s ich hodnotami) a polí a iných štruktúr, ktoré sú podobné poliam. Reťazec je ako pole znakov. Pole celých čísel je uvedené v jednej z predchádzajúcich kapitol. Inštrukcie sa týkajú operačných kódov a ich operandov. Program môže byť napísaný s operačnými kódmi a údajmi zmiešanými v jednej pokračujúcej časti pamäte. Tento prístup má nevýhody, ale neodporúča sa.

Najprv by mal byť napísaný program s inštrukciami a potom s údajmi (množné číslo dátumu sú údaje). Oddelenie medzi pokynmi a údajmi môže byť len niekoľko bajtov. Pre program môžu byť inštrukcie aj dáta v jednej alebo dvoch samostatných sekciách v pamäti.

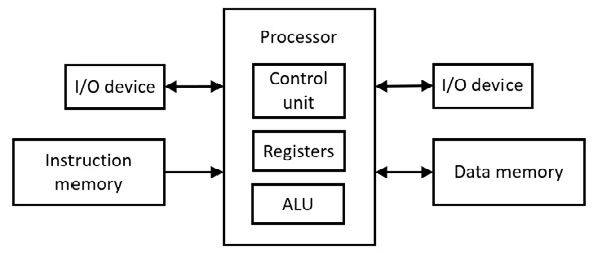

6.6 Harvardská architektúra

Jeden z prvých počítačov sa nazýva Harvard Mark I (1944). Prísna architektúra Harvardu používa jeden adresný priestor pre inštrukcie programu a iný oddelený adresný priestor pre dáta. To znamená, že existujú dve samostatné pamäte. Nasledujúce ukazuje architektúru:

Obrázok 6.71 Harvardská architektúra

Riadiaca jednotka vykoná dekódovanie inštrukcie. Aritmetická logická jednotka (ALU) robí aritmetické operácie s kombinačnou logikou (hradla). ALU tiež robí logické operácie (napr. radenie).

S mikroprocesorom 6502 ide inštrukcia najprv do mikroprocesora (riadiaca jednotka) pred tým, ako údaj (jednotné číslo pre dáta) prejde do registra µP predtým, ako interagujú. Vyžaduje si to aspoň dva hodinové impulzy a nejde o súčasný prístup k inštrukcii a údaju. Na druhej strane, architektúra Harvardu poskytuje súčasný prístup k inštrukciám a dátam, pričom inštrukcia aj údaj vstupujú do µP súčasne (operačný kód do riadiacej jednotky a dátum do registra µP), čím sa ušetrí aspoň jeden hodinový impulz. Toto je forma paralelizmu. Táto forma paralelizmu sa používa v hardvérovej vyrovnávacej pamäti moderných základných dosiek (pozri nasledujúcu diskusiu).

6.7 Vyrovnávacia pamäť

Cache Memory (RAM) je oblasť vysokorýchlostnej pamäte (v porovnaní s rýchlosťou hlavnej pamäte), ktorá dočasne ukladá programové inštrukcie alebo údaje pre budúce použitie. Vyrovnávacia pamäť pracuje rýchlejšie ako hlavná pamäť. Zvyčajne sa tieto inštrukcie alebo dátové položky načítajú z nedávnej hlavnej pamäte a pravdepodobne budú čoskoro potrebné znova. Primárnym účelom vyrovnávacej pamäte je zvýšiť rýchlosť opakovaného prístupu k rovnakým miestam hlavnej pamäte. Aby bol prístup k položkám uloženým vo vyrovnávacej pamäti efektívny, musí byť výrazne rýchlejší ako prístup k pôvodnému zdroju pokynov alebo údajov, ktorý sa označuje ako záložný obchod.

Keď sa používa vyrovnávacia pamäť, každý pokus o prístup k umiestneniu hlavnej pamäte začína hľadaním vyrovnávacej pamäte. Ak je požadovaná položka prítomná, spracovateľ ju okamžite načíta a použije. Toto sa nazýva Cache Hit. Ak je vyhľadávanie cache neúspešné (chyba cache), inštrukcia alebo dátová položka sa musí získať zo záložného úložiska (hlavnej pamäte). V procese získavania požadovanej položky sa do vyrovnávacej pamäte pridá kópia pre predpokladané použitie v blízkej budúcnosti.

Jednotka správy pamäte

Jednotka správy pamäte (MMU) je obvod, ktorý spravuje hlavnú pamäť a súvisiace pamäťové registre na základnej doske. V minulosti to bol samostatný integrovaný obvod na základnej doske; ale dnes je zvyčajne súčasťou mikroprocesora. MMU by mala spravovať aj cache (obvod), ktorá je dnes tiež súčasťou mikroprocesora. Obvod vyrovnávacej pamäte bol v minulosti samostatným integrovaným obvodom.

Statická RAM

Statická RAM (SRAM) má podstatne rýchlejší prístupový čas ako DRAM, aj keď na úkor podstatne zložitejších obvodov. Bitové bunky SRAM zaberajú oveľa viac miesta na matrici integrovaného obvodu ako bunky zariadenia DRAM, ktoré je schopné uložiť ekvivalentné množstvo údajov. Hlavná pamäť (RAM) sa zvyčajne skladá z DRAM (Dynamic RAM).

Vyrovnávacia pamäť zlepšuje výkon počítača, pretože mnohé algoritmy, ktoré vykonávajú operačné systémy a aplikácie, vykazujú referenčnú lokalitu. Referenčná lokalita sa vzťahuje na opätovné použitie údajov, ku ktorým sa nedávno pristupovalo. Toto sa označuje ako dočasné miesto. Na modernej základnej doske je vyrovnávacia pamäť v rovnakom integrovanom obvode ako mikroprocesor. Hlavná pamäť (DRAM) je ďaleko a je prístupná cez zbernice. Referenčná lokalita sa vzťahuje aj na priestorovú lokalitu. Priestorová lokalita súvisí s vyššou rýchlosťou prístupu k údajom z dôvodu fyzickej blízkosti.

Oblasti vyrovnávacej pamäte sú spravidla malé (v počte miest v bajtoch) v porovnaní so záložným úložiskom (hlavnou pamäťou). Zariadenia vyrovnávacej pamäte sú navrhnuté pre maximálnu rýchlosť, čo vo všeobecnosti znamená, že sú zložitejšie a drahšie na bit ako technológia ukladania údajov, ktorá sa používa v záložnom úložisku. Zariadenia s vyrovnávacou pamäťou majú kvôli svojej obmedzenej veľkosti tendenciu sa rýchlo zapĺňať. Keď cache nemá voľné miesto na uloženie nového záznamu, starší záznam sa musí zahodiť. Radič vyrovnávacej pamäte používa politiku nahradenia vyrovnávacej pamäte na výber toho, ktorý záznam vyrovnávacej pamäte bude prepísaný novým záznamom.

Cieľom vyrovnávacej pamäte mikroprocesora je maximalizovať percento nájdenia vyrovnávacej pamäte v priebehu času, čím poskytuje najvyššiu trvalú rýchlosť vykonávania pokynov. Na dosiahnutie tohto cieľa musí logika ukladania do vyrovnávacej pamäte určiť, ktoré inštrukcie a údaje budú umiestnené do vyrovnávacej pamäte a uchované pre budúce použitie.

Logika ukladania do vyrovnávacej pamäte procesora nezaručuje, že údajová položka uložená vo vyrovnávacej pamäti sa po vložení do vyrovnávacej pamäte niekedy znova použije.

Logika ukladania do vyrovnávacej pamäte sa opiera o pravdepodobnosť, že vzhľadom na časovú (časovo sa opakujúcu) a priestorovú (priestorovú) lokalitu je veľmi dobrá šanca, že údaje uložené vo vyrovnávacej pamäti budú prístupné v blízkej budúcnosti. V praktických implementáciách na moderných procesoroch sa prístupy do vyrovnávacej pamäte zvyčajne vyskytujú pri 95 až 97 percentách prístupov do pamäte. Keďže latencia vyrovnávacej pamäte je malým zlomkom latencie DRAM, vysoká miera zásahov do vyrovnávacej pamäte vedie k podstatnému zlepšeniu výkonu v porovnaní s dizajnom bez vyrovnávacej pamäte.

Nejaký paralelizmus s vyrovnávacou pamäťou

Ako už bolo spomenuté, dobrý program v pamäti má inštrukcie oddelené od údajov. V niektorých systémoch vyrovnávacej pamäte je obvod vyrovnávacej pamäte „naľavo“ od procesora a ďalší obvod vyrovnávacej pamäte je „vpravo“ od procesora. Ľavá vyrovnávacia pamäť spracováva pokyny programu (alebo aplikácie) a pravá vyrovnávacia pamäť spracováva údaje rovnakého programu (alebo rovnakej aplikácie). To vedie k lepšiemu zvýšeniu rýchlosti.

6.8 Procesy a vlákna

Počítače CISC aj RISC majú procesy. V softvéri je proces. Program, ktorý je spustený (vykonávaný) je proces. Operačný systém je dodávaný s vlastnými programami. Počas prevádzky počítača sú spustené aj programy operačného systému, ktoré umožňujú počítaču pracovať. Toto sú procesy operačného systému. Používateľ alebo programátor môže písať svoje vlastné programy. Keď je spustený používateľský program, je to proces. Nezáleží na tom, či je program napísaný v jazyku symbolických inštancií alebo vo vysokoúrovňovom jazyku ako C alebo C++. Všetky procesy (používateľ alebo OS) sú riadené iným procesom nazývaným „plánovač“.

Vlákno je ako podproces patriaci do procesu. Proces sa môže spustiť a rozdeliť na vlákna a potom stále pokračuje ako jeden proces. Proces bez vlákien možno považovať za hlavné vlákno. Procesy a ich vlákna sú riadené rovnakým plánovačom. Samotný plánovač je program, keď je rezidentom na disku OS. Keď beží v pamäti, plánovač je proces.

6.9 Viacnásobné spracovanie

Vlákna sa spravujú takmer ako procesy. Multiprocessing znamená spustenie viac ako jedného procesu súčasne. Existujú počítače s iba jedným mikroprocesorom. Existujú počítače s viac ako jedným mikroprocesorom. S jedným mikroprocesorom procesy a/alebo vlákna používajú rovnaký mikroprocesor spôsobom prekladania (alebo časového segmentovania). To znamená, že proces využíva procesor a zastaví sa bez dokončenia. Iný proces alebo vlákno používa procesor a zastaví sa bez dokončenia. Potom ďalší proces alebo vlákno použije mikroprocesor a zastaví sa bez dokončenia. Toto pokračuje, kým všetky procesy a vlákna, ktoré boli zaradené do frontu plánovačom, nebudú mať podiel na procesore. Toto sa označuje ako súbežné multiprocesovanie.

Ak existuje viac ako jeden mikroprocesor, dochádza k paralelnému multiprocesingu, na rozdiel od súbežnosti. V tomto prípade každý procesor spúšťa určitý proces alebo vlákno, ktoré sa líši od toho, čo beží druhý procesor. Všetky procesory na rovnakej základnej doske spúšťajú svoje rôzne procesy a/alebo rôzne vlákna súčasne v paralelnom multiprocesingu. Procesy a vlákna v paralelnom multiprocesingu sú stále riadené plánovačom. Paralelné multiprocesovanie je rýchlejšie ako súbežné multiprocesing.

V tomto bode sa čitateľ môže čudovať, ako je paralelné spracovanie rýchlejšie ako súbežné spracovanie. Je to preto, že procesory zdieľajú (musia používať v rôznych časoch) rovnakú pamäť a vstupné/výstupné porty. No a s využitím cache je celkový chod základnej dosky rýchlejší.

6.10 Stránkovanie

Jednotka správy pamäte (MMU) je obvod, ktorý je blízko mikroprocesora alebo v čipe mikroprocesora. Rieši pamäťovú mapu alebo stránkovanie a ďalšie problémy s pamäťou. Ani 6502 µP, ani počítač Commodore-64 nemajú MMU ako také (hoci v Commodore-64 stále existuje určitá správa pamäte). Commodore-64 spracováva pamäť stránkovaním, kde každá strana je 256 10 bajtov dlhý (100 16 dlhé bajty). Spracovať pamäť stránkovaním nebolo povinné. Stále by to mohlo mať len pamäťovú mapu a potom programy, ktoré sa len hodia do ich rôznych určených oblastí. Stránkovanie je jedným zo spôsobov, ako zabezpečiť efektívne využitie pamäte bez toho, aby ste mali veľa pamäťových sekcií, ktoré nemôžu mať dáta alebo program.

Architektúra počítača x86 386 bola vydaná v roku 1985. Adresová zbernica má šírku 32 bitov. Celkovo teda 2 32 = 4 294 967 296 adresného priestoru je možné. Tento adresný priestor je rozdelený na 1 048 576 stránok = 1 024 KB stránok. Pri tomto počte stránok pozostáva jedna stránka zo 4 096 bajtov = 4 KB. Nasledujúca tabuľka zobrazuje stránky fyzických adries pre 32-bitovú architektúru x86:

| Tabuľka 6.10.1 Fyzické adresovateľné stránky pre architektúru x86 |

||

|---|---|---|

| Základ 16 adries | Stránky | Základ 10 adries |

| FFFFF000 – FFFFFFFF | Strana 1,048,575 | 4 294 963 200 – 4 294 967 295 |

| FFFFE000 – FFFFEFFF | Strana 1,044,479 | 4 294 959 104 – 4 294 963 199 |

| FFFFD000 – FFFFFFFF | Strana 1,040,383 | 4 294 955 008 – 4 294 959 103 |

| | | | |

| | | |

| | | |

| 00002000 – 00002FFF | Strana 2 | 8 192 – 12 288 |

| 00001000 – 00001FFF | Strana 1 | 4 096 – 8 191 |

| 00000000 – 00000FFF | Strana 0 | 0 – 4 095 |

Aplikácia dnes pozostáva z viac ako jedného programu. Jeden program môže zabrať menej ako jednu stranu (menej ako 4096) alebo dve alebo viac strán. Aplikácia teda môže mať jednu alebo viac stránok, pričom každá stránka má dĺžku 4096 bajtov. Prihlášku môžu napísať rôzni ľudia, pričom každá osoba je priradená k jednej alebo viacerým stránkam.

Všimnite si, že stránka 0 je od 00000000H do 00000FFF

strana 1 je od 00001000H do 00001FFFH, strana 2 je od 00002000 H – 00002FFF H , a tak ďalej. Pre 32-bitový počítač sú v procesore dva 32-bitové registre na fyzické adresovanie stránok: jeden pre základnú adresu a druhý pre adresu indexu. Ak chcete získať prístup k umiestneniu bajtov na strane 2, napríklad register pre základnú adresu by mal byť 00002 H čo je prvých 20 bitov (zľava) pre začiatočné adresy stránky 2. Zvyšok bitov v rozsahu 000 H do FFF H sú v registri nazývanom „indexový register“. Takže všetky bajty na stránke sú prístupné jednoduchým zvýšením obsahu v indexovom registri od 000 H do FFF H . Obsah v indexovom registri sa pridá k obsahu, ktorý sa v základnom registri nemení, aby sa získala efektívna adresa. Táto schéma adresovania indexu platí pre ostatné stránky.

Toto však v skutočnosti nie je spôsob, akým je program v assembleri napísaný pre každú stránku. Pre každú stránku programátor napíše kód začínajúci od strany 000 H na stranu FFF H . Keďže kód na rôznych stránkach je prepojený, kompilátor používa indexové adresovanie na spojenie všetkých súvisiacich adries na rôznych stránkach. Predpokladajme napríklad, že strana 0, strana 1 a strana 2 sú pre jednu aplikáciu a každá má 555 H adresy, ktoré sú navzájom prepojené, kompilátor skompiluje takým spôsobom, že keď 555 H zo strany 0 je prístupná, 00000 H bude v základnom registri a 555 H bude v registri indexov. Keď 555 H zo strany 1 je prístupný, 00001 H bude v základnom registri a 555 H bude v registri indexov. Keď 555 H zo strany 2 je prístupný, 00002 H bude v základnom registri a 555H bude v indexovom registri. Je to možné, pretože adresy možno identifikovať pomocou štítkov (premenných). Rôzni programátori sa musia dohodnúť na názve štítkov, ktoré sa majú použiť pre rôzne spojovacie adresy.

Stránka Virtuálna pamäť

Stránkovanie, ako už bolo popísané vyššie, môže byť upravené tak, aby sa zväčšila veľkosť pamäte v technike, ktorá sa nazýva „Page Virtual Memory“. Za predpokladu, že všetky stránky fyzickej pamäte, ako bolo opísané vyššie, majú niečo (inštrukcie a údaje), nie všetky stránky sú momentálne aktívne. Stránky, ktoré momentálne nie sú aktívne, sa odošlú na pevný disk a nahradia sa stránkami z pevného disku, ktoré je potrebné spustiť. Týmto spôsobom sa zvyšuje veľkosť pamäte. Keď počítač pokračuje v prevádzke, stránky, ktoré sa stanú neaktívnymi, sa vymenia za stránky na pevnom disku, čo môžu byť stále stránky odoslané z pamäte na disk. To všetko zaisťuje jednotka správy pamäte (MMU).

6.11 Problémy

Čitateľovi sa odporúča, aby pred prechodom na ďalšiu kapitolu vyriešil všetky problémy v kapitole.

1) Uveďte podobnosti a rozdiely počítačových architektúr CISC a RISC. Uveďte jeden príklad počítača SISC a RISC.

2) a) Aké sú nasledujúce názvy pre počítač CISC z hľadiska bitov: byte, word, doubleword, quadword a double quadword.

b) Aké sú nasledujúce názvy pre počítač RISC z hľadiska bitov: byte, halfword, word a doubleword.

c) Áno alebo Nie. Znamená doubleword a quadword to isté v architektúre CISC aj RISC?

3 a) Pre x64 sa počet bajtov pre inštrukcie v jazyku symbolických inštrukcií pohybuje od čoho do čoho?

b) Je počet bajtov pre všetky inštrukcie v assembleri pre ARM 64 pevný? Ak áno, aký je počet bajtov pre všetky inštrukcie?

4) Uveďte najčastejšie používané inštrukcie v assembleri pre x64 a ich význam.

5) Uveďte najčastejšie používané inštrukcie v jazyku assembleru pre ARM 64 a ich význam.

6) Nakreslite označenú blokovú schému starého počítača Harvard Architecture. Vysvetlite, ako sa jeho pokyny a dátové funkcie používajú vo vyrovnávacej pamäti moderných počítačov.

7) Rozlišujte medzi procesom a vláknom a uveďte názov procesu, ktorý spracováva procesy a vlákna vo väčšine počítačových systémov.

8) Stručne vysvetlite, čo je multiprocesing.

9) a) Vysvetlite stránkovanie ako použiteľné pre architektúru počítača x86 386 µP.

b) Ako možno upraviť toto stránkovanie, aby sa zväčšila veľkosť celej pamäte?